Сімейство процесорів Intel Pentium

- P54CS

- Tillamook

Pentium(вимовляється Пентіум) - торгова маркакількох поколінь мікропроцесорів сімейства x86, що випускаються корпорацією Intel з 22 березня 1993 року. Pentium є процесором Intel п'ятого покоління та прийшов на зміну Intel 80486 (який часто називають просто 486).

Історія

Моделі

Спочатку (22 березня 1993 року) було представлено лише дві моделі, засновані на ядрі P5 із частотами 60 та 66 МГц. Пізніше були випущені продуктивніші процесори Pentium, засновані на вдосконалених ядрах. Крім того, були представлені мобільні версії процесорів та процесори Pentium OverDrive.

| Кодове ім'я ядра | P5 | P54C | P54CS | P55C | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Техпроцес, нм | 800 | 600 | 350 | ||||||||||

| Тактова частота ядра, МГц | 60 | 66 | 75 | 90 | 100 | 120 | 133 | 150 | 166 | 200 | 166 | 200 | 233 |

| Анонсовано | 23 березня 1993 | 10 жовтня 1993 | 7 березня 1994 | 27 березня 1995 | 12 червня 1995 | 4 січня 1996 | 10 червня 1996 | 8 січня 1997 | 2 червня 1997 | ||||

P5

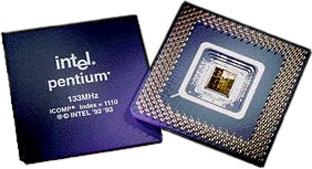

Єдині дві моделі процесорів Pentium першого покоління з тактовою частотою ядра 60 і 66 МГц були анонсовані 23 березня 1993 року.

Процесор випускався в 273-контактному корпусі CPGA, на материнську плату встановлювався в процесорний роз'єм Socket 4 і вимагав живлення напругою 5 В. Частота системної шини (FSB) дорівнювала частоті ядра, тобто множник ядра дорівнював 1,0.

Всі процесори Pentium відносяться до класу SL Enhanced - це означає, що в них передбачено систему SMM, що забезпечує зниження енергоспоживання. Кеш другого рівня розміщувався на материнській платі та міг мати розмір до 1 Мб. Ранні варіанти процесорів, з частотами 60-100 МГц (ядра P5 і P54C), мали помилку в модулі математичного співпроцесора, яка в поодиноких випадках призводила до зменшення точності операції поділу. Цей дефект був виявлений у 1994 році і став відомим як «Pentium FDIV баг».

Процесори на ядрі P5 виготовлялися з використанням 800-нанометрового техпроцесу, за біполярною BiCMOS-технологією. Процесор містить 3,1 млн. транзисторів, а розмір кристала ядра становить 294 мм². Pentium 66 споживає струм 3,2 А і має потужність 16 Вт, що зажадало установки додаткового вентилятора. Виробництво таких процесорів виявилося дуже складним і відсоток виходу придатних кристалів виявився дуже малим. Чимало фахівців, вказуючи на численні недоліки (див.: F0 0f c7 c8) процесорів Pentium першого покоління, не радили купувати дані моделі. Виробництво на якийсь час довелося зупинити. Однак незабаром почалося виробництво вдосконалених процесорів, що базуються на ядрі P54C.

P54C

У процесорах Pentium другого покоління використовується множення тактової частоти, він працює швидше за системну шину. Для вказівки, у скільки разів тактова частота ядра процесора більша за частоту системної шини, використовується множник. У всіх процесорах, заснованих на ядрі P54C, множник дорівнює 1,5.

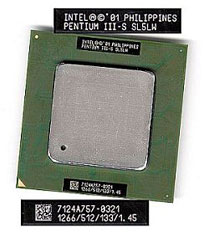

P54CS

Перші процесори, засновані на даному ядрі, було випущено 27 березня 1995 року. По суті, це ядро є ядром P54C, виготовленим з використанням 350-нанометрової біполярної BiCMOS-технології, що дозволило зменшити розмір кристала ядра до 91 мм² (процесори Pentium 120 і 133), однак незабаром, в результаті оптимізації ядра, його розмір вдалося зменшити до 83 мм при тій же кількості транзисторів. При цьому Pentium 200 споживав струм в 4,6 А, а його максимальна енергія, що розсіюється (тепловиділення) становило 15,5 Вт.

P55C

8 січня 1997 були випущені процесори Pentium, засновані на ядрі P5 третього покоління (P55C). Центром розробок та досліджень Intel у Хайфі (Ізраїль) в ядро P55C був доданий новий набір інструкцій, названий MMX (MultiMedia eXtension), що істотно збільшує (від 10 до 60%, залежно від оптимізації) продуктивність комп'ютера в мультимедіа-додатках. В результаті, ці процесори називаються Pentium w/MMX technology (зазвичай скорочується до Pentium MMX). Новий процесор включає пристрій MMX з конвеєрною обробкою команд, кеш L1 збільшений до 32 Кб (16 Кб для даних і 16 Кб для інструкцій). Складається новий процесорз 4,5 млн транзисторів і виробляється за вдосконаленою 280-нанометровою CMOS-технологією з використанням кремнієвих напівпровідників, працює на напрузі 2,8 В. Максимальний споживаний струм дорівнює 6,5 А, тепловиділення дорівнює 17 Вт (для Pentium 233 MMX). Площа кристала у процесорів Pentium MMX дорівнює 141 мм. Процесори випускалися у 296-контактному корпусі типу CPGA або PPGA для Socket 7.

Pentium OverDrive

Випустили кілька поколінь Pentium OverDrive.

- 1995 року вийшов перший Pentium OverDrive (на ядрі P24T). Він був призначений для встановлення в гнізда типу Socket 2 або Socket 3 і працював із напругою живлення 5 В, тобто служив для модернізації систем, які використовують процесор 486 без заміни материнської плати. При цьому даний процесор володів усіма функціями процесора Pentiumпершого покоління (на ядрі P5). Було випущено дві моделі, що працюють на частотах 63 і 83 МГц, старша споживала струм в 2,8 А і мала розсіювану потужність 14 Вт. Через високу вартість цей процесор пішов, не встигнувши з'явитися. І хоча через деякий час (4 березня 1996) на зміну цим процесорам прийшли Pentium ODP5V з частотами 120 і 133 МГц, засновані на ядрі P5T (по суті, являє собою ядро P54CS), вони також не стали популярні.

- 4 березня 1996 року виходить наступна версія Pentium OverDrive – Pentium ODP3V – на ядрі P54CT. Це ядро засноване на ядрі P54CS. Процесор випускався у 320-контактному корпусі CPGA для Socket 5 чи Socket 7.

- 3 березня 1997 виходять дві моделі Pentium ODPMT (з частотами 150 і 166 МГц), побудовані на ядрі P54CTB (аналог P55C). Пізніше, 4 серпня 1997 року, виходять ще дві моделі на тому самому ядрі (з частотами 180 і 200 МГц). Вони випускалися в 320-контактних корпусах CPGA і були призначені для Socket 5 або Socket 7 (Pentium ODPMT-200 MMX – тільки Socket 7).

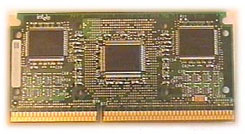

Tillamook

Процесори, засновані цьому ядрі, призначалися для портативних комп'ютерів, використовувалися т. зв. «мобільному модулі» MMC-1 Mobile Module Connector з 280 пінами працювали разом із чіпсетом Intel 430 TX та маючи при цьому 512 КБ кеш-пам'яті на системній платі. Ядро Tillamook (названо на честь міста в штаті Орегон, США), являє собою ядро P55C зі зниженою напругою живлення - модель з частотою 300 МГц працювала з напругою 2,0 В, споживаючи при цьому струм 4,5 А і володіла тепловиділенням 8 4 Вт. Старші моделі (з частотою 233, 266 і 300 МГц) випускалися з використанням 250-нм техпроцесу і мали кристал площею 90 мм², також існували версії зі 166 МГц частотою ядра Моделі 200 і 233 випускалися з серпня 1996 р. , А старша в лінійці модель була представлена в січні 1999 року.

(який часто називають просто 486).

Енциклопедичний YouTube

1 / 4

Why Were Pentium 2"s on Cards? | Nostalgia Nerd

Pentium vs 486 PC (1993)

Armado y desarmado de un CPU Pentium 4, практика d'un estudiante en informática.

Why Pentium Kicks 486 Ass (Pipelines & Cache) | Nostalgia Nerd

Субтитри

Історія

Процесори на ядрі P5 виготовлялися з використанням 800-нанометрового-техпроцесу, за біполярною BiCMOS-технологією. Процесор містить 3,1 млн. транзисторів, а розмір кристала ядра становить 294 мм². Pentium 66 споживає струм 3,2 А і має потужність 16 Вт, що зажадало установки додаткового вентилятора. Виробництво таких процесорів виявилося дуже складним і відсоток виходу придатних кристалів виявився дуже малим. Багато фахівців, вказуючи на численні недоліки (див.: F0 0f c7 c8) процесорів Pentium першого покоління, не радили купувати дані моделі. Виробництво на якийсь час довелося зупинити. Однак незабаром почалося виробництво вдосконалених процесорів, що базуються на ядрі P54C.

P54C

У процесорах Pentium другого покоління використовується множення тактової частоти, він працює швидше за системну шину. Для вказівки, у скільки разів тактова частота ядра процесора більша за частоту системної шини, використовується множник. У всіх процесорах, заснованих на ядрі P54C, множник дорівнює 1,5.

P54CS

Перші процесори, засновані на даному ядрі, були випущені 27 березня 1995 року. По суті, це ядро є ядром P54C, виготовленим з використанням 350-нанометрової біполярної BiCMOS-технології, що дозволило зменшити розмір кристала ядра до 91 мм² (процесори Pentium 120 і 133), однак незабаром, в результаті оптимізації ядра, його розмір вдалося зменшити до 83 мм при тій же кількості транзисторів. При цьому Pentium 200 споживав струм в 4,6 А, а його максимальна енергія, що розсіюється (тепловиділення) становило 15,5 Вт.

P55C

8-січня 1997-року були випущені процесори Pentium, засновані на ядрі P5 третього покоління (P55C). Центром розробок та досліджень Intel у Хайфі (Ізраїль) в ядро P55C був доданий новий набір інструкцій, названий MMX (MultiMedia eXtension), що істотно збільшує (від 10 до 60%, залежно від оптимізації) продуктивність комп'ютера в мультимедіа-додатках. В результаті, ці процесори називаються Pentium w/MMX technology (зазвичай скорочується до Pentium MMX). Новий процесор включає пристрій MMX з конвеєрною обробкою команд, кеш L1 збільшений до 32 Кб (16 Кб для даних і 16 Кб для інструкцій). Складається новий процесор з 4,5 млн транзисторів і виробляється за вдосконаленою 280-нанометровою CMOS-технологією з використанням кремнієвих напівпровідників, працює на напрузі 2,8 В. Максимальний струм споживання дорівнює 6,5 А, тепловиділення дорівнює 17 Вт (для Pentium 233 ). Площа кристала у процесорів Pentium MMX дорівнює 141 мм. Процесори випускалися у 296-контактному корпусі типу CPGA або PPGA для Socket 7.

Pentium OverDrive

Випустили кілька поколінь Pentium OverDrive.

- У 1995-му році вийшов перший Pentium OverDrive (на ядрі P24T). Він був призначений для установки в гнізда типу Socket 2 або Socket 3 і працював з напругою живлення 5 В, тобто служив для модернізації систем, що використовують процесор 486 без заміни материнської плати. При цьому цей процесор мав усі функції процесора Pentium першого покоління (на ядрі P5). Було випущено дві моделі, що працюють на частотах 63 і 83 МГц, старша споживала струм в 2,8 А і мала розсіювану потужність 14 Вт. Через високу вартість цей процесор пішов, не встигнувши з'явитися. І хоча через деякий час (4 березня 1996) на зміну цим процесорам прийшли Pentium ODP5V з частотами 120 і 133 МГц, засновані на ядрі P5T (по суті, являє собою ядро P54CS), вони також не стали популярні.

- 4 березня 1996 року виходить наступна версія Pentium OverDrive - Pentium ODP3V - на ядрі P54CT. Це ядро засноване на ядрі P54CS. Процесор випускався у 320-контактному корпусі CPGA для Socket 5 чи Socket 7.

- 3 березня 1997 року виходять дві моделі Pentium ODPMT (з частотами 150 і 166 МГц), побудовані на ядрі P54CTB (аналог P55C). Пізніше, 4 серпня 1997 року, виходять ще дві моделі на тому самому ядрі (з частотами 180 і 200 МГц). Вони випускалися в 320-контактних корпусах CPGA і були призначені для Socket 5 або Socket 7 (Pentium ODPMT-200 MMX – тільки Socket 7).

Tillamook

Процесори, засновані цьому ядрі, призначалися для портативних комп'ютерів, використовувалися т.зв. "мобільному модулі" MMC-1 Mobile Module Connector з 280 пінами працювали разом із чіпсетом Intel 430 TX і маючи при цьому 512 КБ кеш-пам'яті на системній платі. Ядро Tillamook (названо на честь міста в штаті Орегон, США), являє собою ядро P55C зі зниженою напругою живлення - модель з частотою 300 МГц працювала з напругою 2,0 В, споживаючи при цьому струм 4,5 А і володіла тепловиділенням 8 4 Вт. Старші моделі (з частотою 233, 266 і 300 МГц) випускалися з використанням 250-нм техпроцесу і мали кристал площею 90 мм², також існували версії зі 166 МГц частотою ядра Моделі 200 і 233 випускалися з серпня 1996 р. , А старша в лінійці модель була представлена в січні 1999 року.

За більш ніж 10 років свого існування процесори Pentium фірми Intel пройшли величезний шлях. Тільки тактова частота зросла більш ніж 53 разу, з 60 МГц до 3200 МГц. Також Intel є автором багатьох розробок, які вже потім використовували такі компанії як AMD і VIA.

Усього за ці 10 років було випущено такі сімейства процесорів:

- 1993 рік - Intel Pentium

- 1995 рік - Intel Pentium PRO

- 1997 рік - Intel Pentium MMX

- 1997 рік - Intel Pentium II

- 1999 рік - Intel Pentium !!!

- 2000 рік - Intel Pentium 4

А тепер розглянемо кожне з них докладніше.

Все почалося 22 березня 1993 року. Саме тоді Intel представляє перші процесори під торговою маркою Pentium, яка на довгі роки стала синонімом слова процесор.

Це був перший процесор із двоконвеєрною структурою. Носив кодове ім'я P5. Мав тактові частоти 60 та 66 МГц. Частота шини збігалася із тактовою частотою процесора. Процесори містили понад 3.1 млн. транзисторів та випускалися за технологією 0.80 мкм, а пізніше – 0.60 мкм. Розмір кешу першого рівня L1 становив 16 Кб - 8 Кб на дані та 8 Кб на інструкції, тоді як кеш другого рівня розміщувався на материнській платі і міг мати об'єм до 1 Мб. Процесор випускався для гнізда Socket 4.

Через рік, у березні 1994 року, Intel випускає друге покоління Pentium (ядро P54).

Процесор мав частоти від 75 до 200 МГц. Частота шини 50-66 МГц. Розмір кешу L1 залишився тим самим – 16 Кб (8 Кб на дані та 8 Кб на інструкції). Кеш другого рівня залишився на материнській платі і міг мати об'єм до 1 Мб. При виробництві цього процесора Intel застосовує досконаліший техпроцес 0.50 мкм. Процесор містив понад 3,3 млн. транзисторів. Випускався для рознімання Socket 5, пізніше Socket 7.

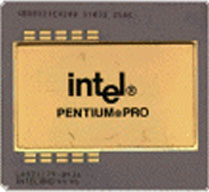

Pentium PRO

1 листопада 1995 року, випуском процесора Pentium PRO (кодове ім'я) P6), розпочався відлік шостого покоління процесорів. Від попереднього покоління їх відрізняло застосування технології динамічного виконання – зміни порядку виконання інструкцій та архітектура подвійної незалежної шини. Додалася ще одна шина, яка з'єднує процесор із кешем другого рівня, який вбудований у ядро. В результаті цього вперше було застосовано кеш L2, що працює на частоті процесора. Початковий розмір кешу L2 - 256 Кб; до 18 серпня 1997 досяг 1024 Кб. Максимальний розмір – 2048 Кб. Кеш першого рівня залишився тим самим: 8 Кб + 8 Кб. Мав тактові частоти 150, 166, 180, 200 МГц.

Процесори Pentium PRO випускалися в корпусах SPGA (Staggered Pin Grid Array) із матрицею штиркових висновків. В одному корпусі було встановлено два кристали – ядро процесора та кеш другого рівня власного виготовлення. Встановлювався в Socket 8 з можливістю поєднати до 4-х процесорів для симетричної мультипроцесорної обробки. Шина 60-66 МГц. При 32-бітових обчисленнях і багатозадачності значно перевершував за продуктивністю Pentium, але у 16-бітних додатках програвав йому. Процесор 150 МГц вироблявся з використанням техпроцесу 0.60 мкм, старші моделі – 0.35 мкм. Pentium PRO складався з більш як 5.5 млн. транзисторів, плюс від 15.5 до 31 млн. включав кеш. Pentium MMX

8 січня 1997 року відбувся випуск процесора Pentium w/MMX technology(кодове ім'я P55), що є продовженням лінійки Pentium, в якому вперше був реалізований новий набір з 57 команд MMX (Multi Media eXtention), що істотно збільшує продуктивність комп'ютера в мультимедіа-додатках (від 10 до 60%, залежно від оптимізації).

Випускався з тактовими частотами 166, 200 та 233 МГц. Працював на 66 МГц шині. Порівняно з Pentium, було вдвічі збільшено розмір кешу першого рівня, що становить 32 Кб. Як і в попередніх версіях, був застосований роздільний кеш: 16 Кб на дані і 16 Кб на інструкції. Такий поділ (і розмір) кешу L1 став своєрідним стандартом на довгі роки. Кеш другого рівня, як і в попередника, залишився на материнській платі і міг мати об'єм до 1 Мб. Процесори випускалися за 0.35 мкм технології та складалися з 4.5 млн. транзисторів. Розрахований на Socket 7.

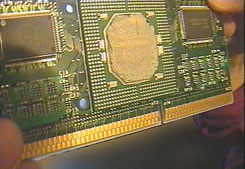

Pentium II

Перші процесори під назвою Pentium II з'явилися 7 травня 1997 року. Ці процесори поєднують архітектуру Pentium PRO та технологію MMX. У порівнянні з Pentium Pro подвоєно розмір первинного кешу (16 Кб + 16 Кб). У процесорі використовується нова технологія корпусів - картридж з друкованим крайовим роз'ємом, на який виведено системну шину: S.E.C.C (Single Edge Contact Cartridge). Випускався у конструктиві Slot 1, що природно зажадало апгрейду старих системних плат. На картриджі розміром 14 x 6.2 x 1.6 см встановлена мікросхема ядра процесора (CPU Core), кілька мікросхем, що реалізують вторинний кеш, та допоміжні дискретні елементи (резистори та конденсатори).

Такий підхід можна вважати кроком тому – у Intel вже було відпрацьовано технологію вбудовування в ядро кешу другого рівня. Але в такий спосіб можна було використовувати мікросхеми пам'яті сторонніх виробників. Свого часу Intel вважала такий підхід перспективним на найближчі 10 років, хоча через нетривалий час відмовляється від нього.

У той самий час зберігається незалежність шини вторинної кеш-пам'яті, що тісно пов'язані з ядром процесора власної локальної шиною. Частота цієї шини була вдвічі менша за частоту ядра. Отже Pentium II мав великий кеш, що працює на половинній частоті процесора.

Перші процесори Pentium II (кодова назва Klamath), що з'явилися 7 травня 1997, налічували близько 7.5 млн. транзисторів тільки в процесорному ядрі і виконувались за технологією 0.35 мкм. Вони мали тактові частоти ядра 233, 266 та 300 МГц при частоті системної шини 66 МГц. При цьому вторинний кеш працював на половинній частоті ядра та мав об'єм 512 Кб. Для цих процесорів був розроблений Slot 1, що за складом сигналів сильно нагадує Socket 8 для Pentium Pro. Однак Slot 1 дозволяє об'єднувати лише пару процесорів для реалізації симетричної мультипроцесорної системи або системи з надмірним контролем функціональності (FRC). Так що цей процесор є більш швидким Pentium Pro з підтримкою MMX, але з урізаною підтримкою мультипроцесорності.

26 січня 1998 вийшов процесор з лінійки Pentium II з назвою ядра - Deschutes. Від Klamathвідрізнявся більш тонким технологічним процесом – 0.25 мкм та частотою шини 100 МГц. Мав тактові частоти 350, 400, 450 МГц. Випускався в конструктиві S.E.C.C, який у старших моделях був змінений на S.E.C.C.2 - кеш з одного боку від ядра, а не з двох, як у стандартному Deschutes та змінене кріплення кулера. Останнє ядро, що офіційно застосовувалося в процесорах Pentium II, хоча останні моделі Pentium II 350-450 йшли з ядром, яке вже більше нагадувало Katmai - тільки, природно, з обрізаним SSE. Залишилась підтримка MMX. Кеш першого рівня – ті самі 32 Кб (16 + 16). Кеш другого рівня також не змінився - 512 Кб, що працюють на половинній частоті. Процесор складався з 7.5 млн транзисторів і випускався для роз'єму Slot 1.

Pentium II OverDrive- так називався процесор, що вийшов 11 серпня 1998 для апгрейду Pentium PRO на старих материнських платах, і працюючий у роз'ємі Socket 8).

Носив кодове ім'я P6T. Мав частоту 333 МГц. Кеш першого рівня – 16 Кб на дані + 16 Кб на інструкції, кеш другого рівня мав розмір 512 Кб та був інтегрований у ядро. Працював на частоті процесора. Шина 66 МГц. Утримував 7.5 млн. транзисторів та вироблявся за техпроцесом 0.25 мкм. Підтримував набір інструкцій MMX.

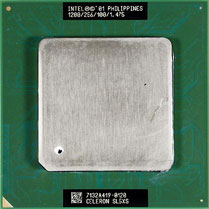

Новою гілкою у напрямку технології мікропроцесорів для Intel був випуск паралельних основним, "полегшених" та здешевлених варіантів. Такою є серія Celeron. 15 квітня 1998 року був представлений перший процесор, що має назву Celeronта працюючий на тактовій частоті 266 МГц.

Кодове ім'я Covington. Цей процесор є "обрізаним" Pentium II. Celeron побудований на базі ядра Deschutesбез кешу другого рівня. Що, звичайно, позначилося на його продуктивності. Зате розганявся він просто чудово (від півтора до двох разів). Якщо розгін PentiumІІ обмежувала максимальна частота кешу, то тут його просто не було!

Celeron працював на шині 66 МГц і повторював усі основні характеристики свого предка – Pentium II Deschutes: кеш першого рівня – 16 Кб + 16 Кб, MMX, техпроцес 0.25 мкм. 7,5 млн. транзисторів. Процесор випускався без захисного картриджа – конструктив – S.E.P.P (Single Edge Pin Package). Роз'єм - Slot 1.

Починаючи з частоти 300 МГц, з'явилися процесори Celeron з інтегрованим у ядро кешем другого рівня, що працює на частоті процесора розміром 128 Кб. Кодове ім'я Mendocino. Вийшов 8 серпня 1998 року. Завдяки повношвидкісному кешу має високу продуктивність, порівнянну з Pentium II (за умови однакової частоти системної шини). Випускалися із тактовими частотами від 300 до 533 МГц. 30 листопада 1998 року вийшов варіант процесора з конструктивом P.P.G.A (Plastic Pin Grid Array), який працював у роз'ємі Socket 370.

До 433 МГц випускався у двох конструктивах: S.E.P.P та P.P.G.A. Деякий час паралельно існували Slot-1 (266 – 433 МГц) та Socket-370 (300A – 533 МГц) варіанти, зрештою, перший був плавно витіснений останнім.

Новий Celeron був кроком до Pentium!!!, але оскільки працював на шині 66 МГц, не міг показати всі переваги інтегрованого високошвидкісного кешу. Оскільки кеш був інтегрований у ядро, значно збільшилася кількість транзисторів, у тому числі складається процесор - 19 млн. Техпроцес залишився тим самим – 0.25 мкм.

Для потужних комп'ютерівпризначено сімейство Xeon. Pentium II Xeon – серверний варіант процесора Pentium II, який прийшов на зміну Pentium PRO. Вироблявся на ядрі Deschutesі відрізнявся від Pentium II більш швидкою (повношвидкісною) та більш ємною (є варіанти з 1 або 2 Мб) кеш-пам'яттю другого рівня та конструктивом. Випускався в конструктиві SEC для Slot 2. Це теж крайовий роз'єм, але з 330 контактами, регулятором напруги VRM, запам'ятовуючим пристроєм EEPROM. Чи здатний працювати в мультипроцесорних конфігураціях. Було випущено 29 червня 1998 року.

Кеш другого рівня, як і Pentium PRO, повношвидкісний. Тільки тут він знаходиться на одній платі із процесором, а не інтегрований у ядро. Кеш першого рівня - 16 Кб + 16 Кб. Частота шини – 100 МГц. Підтримував набір інструкцій MMX. Процесор працював на частотах 400 та 450 МГц. Випускався із застосуванням техпроцесу 0.25 мкм. та містив 7.5 млн. транзисторів.

У цьому розвиток лінійки Pentium II закінчується. Починаючи з Pentium II, Intel виділяє три основні напрямки у виробництві процесорів: Pentium– високопродуктивний процесор для робочих станцій та домашнього застосування, Celeron– бюджетний варіант пентіуму для офісу чи будинку, Xeon- серверний варіант, що має підвищену продуктивність.

Pentium !!!

Перші процесори з назвою Pentium! мало чим відрізнялися від Pentium II. Вони працювали на такій же шині з частотою 100 МГц (пізніше, з 27 вересня 1999, з'явилися моделі, що працюють на шині 133 МГц), випускалися в конструктиві S.E.C.C. 2 і були розраховані на встановлення Slot 1.

Кеш пам'ять залишилася колишньою: L1 - 16 Кб + 16 Кб. L2 - 512 Кб, розміщені на процесорній платі, та працюють на половинній частоті процесора. Головною відмінністю є розширення набору SIMD-інструкцій – SSE (Streaming SIMD Extensions). Також розширено набір команд MMX та вдосконалено механізм потокового доступу до пам'яті. Кодове ім'я ядра Katmai. Вийшов 26 лютого 1999 року. p align="justify"> Процесор працював на частотах 450-600 МГц, містив 9.5 млн. транзисторів. Також як попередник – Pentium II Deschutes, випускався із застосуванням техпроцесу 0.25 мкм.

Coppermine- Так називалося наступне ядро процесора Pentium !!!, що прийшло на зміну Katmai 25 жовтня 1999 року. По суті саме Coppermine є новим процесором, а не доробкою Deschutes. Новий процесор мав повношвидкісний інтегрований у ядро кеш другого рівня розміром 256 Кб (Advanced Transfer Cache).

Випускався із використанням техпроцесу 0.18 мкм. Утончення технології з 0.25 до 0.18 мкм дозволило розмістити на ядрі більша кількістьтранзисторів і тепер їх стало 28 млн., проти 9.5 млн. у старому Katmai. Щоправда, переважна більшість нововведених транзисторів належить до інтегрованого L2-кешу. L1 кеш залишився без змін. Підтримував набори команд MMX та SSE. Спочатку випускався у конструктиві S.E.C.C. 2, але так як кеш тепер вбудований в ядро процесора, процесорна плата виявилася непотрібною, і лише підвищувала вартість процесора. Тому невдовзі процесори стали виходити у конструктиві FC-PGA (Flip-Chip PGA). Як і Celeron Mendocino, вони працювали у роз'ємі Socket 370.

Щоправда, зі старими материнськими платами була обмежена сумісність. Так як тепер процесор працював на високих тактових частотах, ядро було розташоване зверху, і мало безпосередній контакт з радіатором. Coppermine був останнім процесором для Slot 1. Працював на шині 100 та 133 МГц (в назві процесора 133-а шина позначалася буквою B, Наприклад - Pentium !!! 750B). Процесори з ядром Coppermine працювали на тактових частотах із 533 до 1200 МГц. Перші спроби випустити процесор на цьому ядрі з частотою 1113 МГц закінчилися невдачею, тому що він у граничних режимах працював дуже нестабільно, і всі процесори з цією частотою були відкликані – цей інцидент сильно підмочив репутацію Intel.

Ядро Tualatinприйшло на зміну Coppermine 21 червня 2001 року. У цей час на ринку вже були перші процесори Pentium 4, і новий процесор був призначений для випробування нової 0.13 мкм. технології, а також для того, щоб заповнити нішу високопродуктивних процесорів, так як продуктивність перших Pentium 4 була досить низькою. Tualatin - це початкова назва глобального проекту Intel із перекладу виробництва процесорів на 0.13-мікронну технологію. Самі процесори з новим ядром стали першими продуктами, що з'явилися цього проекту.

Змін у самому ядрі небагато – додалася лише технологія "Data Prefetch Logic". Вона підвищує продуктивність, завантажуючи дані, необхідні додатку в кеш. Крім цього відмінність цих ядер полягає у використаній технології виробництва - Coppermine виготовляється за технологією 0.18 мкм, а Tualatin по 0.13 мкм. Роз'єм для нового процесора залишився колишнім - Socket 370, а ось конструктив змінився на FC-PGA 2, який використовувався в процесорах Pentium 4. Від старого FC-PGA він в першу чергу відрізняється тим, що ядро вкрите теплорозсіювальною пластиною, яка також захищає його від пошкодження під час встановлення радіатора.

З випуском Tualatin, лінійка Pentium !!! "розпалася" на два класи - настільних та серверних процесорів. У перших обсяг L2-кешу так і залишився рівним 256 Кб, у других – подвоївся до 512 Кб; також у настільної версії нового P-III (так званого Desktop Tualatin) була підтримка SMP. Кеш першого рівня - 16 Кб + 16 Кб. Слід сказати, що Desktop Tualatin проіснував недовго: він поставлявся тільки великим збирачам ПК, і був вилучений з ринку, щоб не складати конкуренцію Pentium 4. А ось Pentium !!!-S, серверна версія процесора, повинен був зайняти нішу потужних серверних процесорів, оскільки продуктивності процесорів Xeon вже не вистачало, а Pentium 4 у відсутності підтримки SMP, та й взагалі показував досить низьку продуктивність.

Як було зазначено вище, процесори Tualatin випускалися із застосуванням досконалішого 0.13 мкм. Техпроцес, працювали на шині з частотою 133 МГц і складалися з 44 млн. транзисторів. Підтримували набори інструкцій MMX та SSE. Процесор працював на частотах від 1 ГГц до 1.33 ГГц (Desktop Tualatin) і від 1.13 ГГц до 1.4 ГГц (серверний варіант).

Нещодавно я дізнався досить цікаву інформацію - виявляється Intel розробляла процесор, який повинен був бути продовженням лінійки Pentium !!!. Цей процесор був заснований на модернізованому ядрі Tualatin із застосуванням 0.13 мкм. техпроцесу. Основними його відмінностями від звичайного Tualatin був збільшений до 1024 Кб. кеш другого рівня та системна шина з частотою 166 МГц! Частоти мали досягати як мінімум 2.0 ГГц. Але Intel, роблячи ставку на процесор Pentium 4, цурається нового Tualatin. Адже якщо навіть Celeron Tualatin, розігнаний до частот порядку 1.7 ГГц, з легкістю конкурує не тільки з Celeron Willamette, але і з Pentium 4, то новий Tualatin, оснащений величезним кешем і швидкою шиною не залишав би їм жодного шансу.

Після виходу процесорів Pentium!!!, Intel, щоб не втрачати позиції на ринку бюджетних процесорів, продовжила випуск лінійки Celeron. Тепер це були абсолютно інші процесори - Intel повторює досвід створення перших процесорів під назвою Celeron: використовує ядро процесора Pentium !!! з обрізаним до 128 кб кешем другого рівня та повільною шиною 66 МГц.

29 березня 2000 року з'являються перші процесори Celeron на ядрі Coppermine 128або Coppermine Lite.

Як видно з назви, процесор виконаний на ядрі Coppermine з удвічі зменшеним кешем другого рівня. Як і старший брат – Pentium!!! Coppermine, новий Celeron, має набір додаткових команд SSE, швидку вбудовану кеш-пам'ять і виробляється за тією ж технологічною нормою (0.18 мкм.), відрізняючись тільки об'ємом кешу другого рівня – 128 Кб проти 256 Кб у Pentium! (Прикріше те, що кеш-то в процесорі фізично присутній, він просто відключений). Працює в тому ж роз'єм Socket 370.

Перші процесори з'явилися із частотою 566 МГц і працювали на шині 66 МГц. Пізніше, 3 січня 2001 року, з виходом 800 МГц версії, Celeron переходить на швидшу 100 МГц шину. Максимальна частота цих процесорів становила 1100 МГц. Кеш першого рівня: 32 Кб (16 Кб на дані та 16 Кб на інструкції). Процесор складався із 28.1 млн. транзисторів.

Ще ніколи Celeron не був такий близький до процесора Pentium. Від Pentium !!! Desktop Tualatin він відрізнявся лише повільнішою 100 МГц шиною. Загалом, залишивши незмінним обсяг кешу другого рівня та знизивши частоту FSB до 100 МГц біля ядра Tualatin для desktop застосування, Intel випустила "новий Celeron". Процесори випускалися з тактовими частотами від 900 МГц до 1400 МГц, складалися з 44 млн транзисторів, підтримували MMX, SSE. Техпроцес 0.13 мкм. Випускалися в конструктиві FC-PGA 2 для роз'єму Socket 370.

З виходом Pentium !!! Intel продовжує випускати серверні процесорина базі нового покоління Pentium. 17 березня 1999 року вийшов перший процесор з лінійки Pentium !!! Xeon.

Кодова назва ядра Tanner. Був збудований на базі Pentium !!! Katmai. Містив 512, 1024 чи 2048 Кб повношвидкісний кеш пам'яті другого рівня. Кеш першого рівня – 16 Кб + 16 Кб. Випускався із частотами 500 і 550 МГц із застосуванням 0.25 мкм. техпроцесу і складався з 9.5 млн. транзисторів. Працював на 100 МГц системній шині. Випускався в конструктиві SEC для Slot 2. Був призначений для використання в двох-, чотири-, восьмипроцесорних (і більше) серверах і робочих станціях.

З переходом Pentium !!! на нове ядро 25 жовтня 1999 з'явилася і модифікація процесора Xeon з новим ядром Cascades. По суті це було модернізоване ядро Coppermine. Процесор мав від 256 КБ до 2048 Кб кеш пам'яті другого рівня, працював на частотах системної шини 100 та 133 МГц (залежно від версії). Випускалися процесори із частотами від 600 до 900 МГц. Процесори з частотою 900 МГц з перших партій перегрівалися та їх постачання було тимчасово припинено. Як і попередник, Xeon Cascades був розрахований на установку в роз'єм Slot 2. Випускався із застосуванням 0.18 мкм. техпроцесу та складався з 28.1 млн. транзисторів. Міг працювати у двох-, чотири- та восьмипроцесорних серверах та робочих станціях.

На базі ядра Tualatinпроцесори Xeon не випускалися. Їхнє місце зайняв Pentium !!!-S, про який я розповідав вище. Процесори Xeonпідтримували набори команд MMX та SSE.

Pentium 4

Зіткнувшись із безліччю проблем при спробі збільшити частоту процесора Pentium !!! на ядрі Coppermine вище 1 ГГц, інженери Intel зрозуміли, що стара архітектура процесорів, що не змінювалася з часів Pentium Pro, потребує радикальних змін. І хоча перехід виробництва на 0.13 мкм допоможе Pentium! ще близько року цілком гідно виконувати свою роботу, потенціал цієї архітектури вже практично вичерпано і компанія для своїх нових 32-розрядних процесорів розробила нову архітектуру, яку назвала Intel NetBurst Micro-Architecture. Щоб процесори могли працювати на частотах порядку кількох гігагерц, Intel збільшує довжину конвеєра Pentium 4 до 20 ступенів (Hyper Pipelined Technology) за рахунок чого вдалося навіть при технологічних нормах 0,18 мкм домогтися роботи процесора на частоті в 2 ГГц. Однак через збільшення довжини конвеєра час виконання однієї команди в процесорних тактах також сильно збільшується. Тому компанія сильно попрацювала над алгоритмами передбачення переходів (Advanced Dynamic Execution).

Кеш 1-го рівня в процесорі зазнав значних змін. На відміну від Pentium !!!, кеш якого міг зберігати команди та дані, Pentium 4 має лише 8 Кб кеш даних. Команди зберігаються в так званому Trace Cache. Там вони зберігаються у декодованому вигляді, тобто. у вигляді послідовності мікрооперацій, що надходять для виконання у виконавчі пристрої процесора. Місткість цього кешу становить 12000 мікрооперацій.

Також у новому процесорі було розширено набір команд - SSE2. До 70 інструкцій SSE додалися ще 144 нові інструкції. Однією з безлічі інновацій була абсолютно нова 100 МГц шина, що передає по 4 пакети даних за такт - QPB (Q uad P umped B us), що дає результуючу частоту 400 МГц.

Першим з лінійки Pentium 4 був процесор із ядром Willamette 423.

З'явившись 20 листопада 2000 з частотами 1.4 і 1.5 ГГц, ці процесори, виготовлені із застосуванням техпроцесу 0.18 мкм, досягли частоти 2 ГГц. Процесор встановлювався у новий роз'єм Socket 423 і випускався у конструктиві FC-PGA 2. Складався із 42 млн. транзисторів.

Кеш 2-го рівня залишився колишнього обсягу – 256 Кб. Ширина шини кешу L2 становить 256 біт, але латентність кешу зменшилася вдвічі, що дозволило досягти пропускної спроможності кеша в 48 Гб при частоті 1.5 ГГц.

Так як архітектура нового процесора була орієнтована насамперед на зростання частоти, то не дивно, що перші процесори Pentium 4 показують вкрай низьку продуктивність. У більшості завдань 1.4 ГГц процесор поступався Pentium !!! Coppermine, що працює на частоті 1000 МГц.

Пізніше, 27 серпня 2001 року, з'явилися процесори з ядром Willametteпризначені для встановлення в новий роз'єм - Socket 478. Процесор повторював усі характеристики свого предка, за винятком конструктиву - mPGA та роз'єму Socket 478.

Попередній форм-фактор Socket 423 був "перехідним" і Intel надалі не має наміру його підтримувати. Розміри процесора зменшилися завдяки тому, що тепер висновки зроблено безпосередньо під ядром процесора. Цей процесор, як і попередник, працював на частотах від 1,4 до 2,0 ГГц.

Northwood- так називається наступне ядро, на якому і досі випускаються процесори Pentium 4.

Перехід до 0.13 мкм. техпроцес дозволив ще більше нарощувати тактову частоту, і збільшити кеш другого рівня до 512 Кб. Збільшилася і кількість транзисторів, які становлять процесор - тепер їх стало 55 млн. Природно, що залишилася підтримка наборів інструкцій MMX, SSE та SSE2.

Перші процесори на ядрі Northwood з'явилися 7 серпня 2001 з частотою 2.0 ГГц і частотою системної шини 400 МГц (4 * 100 МГц). На сьогоднішній день, процесори Northwood працюють на частотах від 1.6 до 3.2 ГГц. Щоб не виникало плутанини з процесорами, що працюють на однакових частотах, але з різним ядром Intel знову застосовує буквене маркування. Наприклад, Pentium 1.8 A, де буква Aвказує на нове ядро та збільшений кеш другого рівня.

6-го травня 2002 року Intel випускає процесор на базі ядра Northwood з частотою системної шини 533 МГц (4 * 133 МГц) і тактовою частотою 2.26 ГГц. Так як моделі з частотою шини 400 МГц випускалися з частотами до 2.6 ГГц, то й тут було застосовано буквене маркування. Як і в процесорах Pentium! наявність 133 МГц шини позначалося буквою B. Наприклад, Pentium 4 2.4 B.

Але Intel не зупиняється на досягнутому, і 14 квітня 2003 випускає процесор на тому ж ядрі Northwood, але вже з частотою системної шини 800 МГц (4 * 200 МГц) і тактовою частотою 3.0 ГГц. Пізніше процесори з 800 МГц системною шиною стали випускатися з меншими частотами - від 2.4 ГГц. Для позначення нової шини у маркуванні процесора з'являється буква C. Наприклад, Pentium 4 2.4 C. (Таким чином, є три модифікації процесора 2.4 ГГц з різними частотами шини, що розрізняються у 2 рази!)

Усі процесори із частотою системної шини 800 МГц підтримують нову технологію HT, що розшифровується як Hyper-Threading.

Pentium 4 HT

14 листопада 2002 року був випущений процесор Pentium 4 із частотою 3.06 ГГц та частотою системної шини 533 МГц із підтримкою нової технології Hyper-Threading.

Один фізичний процесор з Hyper-Threading бачиться системою як два, що дозволяє оптимізувати завантаження його ресурсів та підвищити продуктивність. Принцип дії Hyper-Threading ґрунтується на тому, що в кожний момент часу лише частина ресурсів процесора використовується під час виконання програмного коду. Невикористовувані ресурси також можна завантажити роботою - наприклад, задіяти для паралельного виконання ще однієї програми (чи іншого потоку цієї програми).

HT – це не справжня багатопроцесорність, адже кількість блоків, що безпосередньо виконують команди, не змінилася. Підвищився лише ККД їхнього використання. Тому чим краще оптимізована конкретна програма під HT, тим вище буде виграш у продуктивності. За даними Intel, перевага від HT може досягати 30%, у той час як блоки, що її реалізують, займають менше 5% загальної площі кристала Pentium 4. Втім, навіть ідеально оптимізовані програми можуть, наприклад, звертатися до даних, яких немає в кеш -Пам'яті процесора, змушуючи його простоювати. Якщо сама архітектура NetBurst була розрахована на підвищення кількості мегагерц, то Hyper-Threading навпаки розрахований на підвищення виконуваної роботи за один такт.

Однією з причин досить пізнього уявлення Hyper-Threading у Pentium 4 (підтримка існує не тільки в ядрі Northwood, але навіть у Willamette, проте була заблокована) була відносно невелика поширеність Windows XP - єдиної ОС сімейства Windows, що повноцінно підтримує нову технологію. Також технологію має підтримувати чіпсет та BIOS системної плати.

На сьогоднішній день технологію Hyper-Threading підтримує процесор Pentium 4 3.06 ГГц із частотою системної шини 533 МГц, а також усі процесори із частотою шини 800 МГц.

Після випуску Pentium 4 Willamette для роз'єму Socket 478 з метою витіснення з ринку процесорів для Socket 370, а також, бажаючи зайняти нішу бюджетних процесорів (де до цього був Celeron Tualatin), Intel випускає Celeron на базі ядра Willamette 128.

Ядро Willamette 128 архітектурно нічим не відрізняється від ядра Pentium 4 Willamette. Організація кешу та алгоритми його роботи не змінилися, єдина відмінність полягає у розмірі - 128 Кб кешу другого рівня замість 256 Кб в оригінальному Pentium 4 Willamette.

Звичайно, збережений і форм-фактор Socket 478, який Intel збирається використовувати ще довго. Таким чином, Intel перекладає свої процесори на одну платформу, так що при подальшому апгрейді не доведеться змінювати разом з процесором і материнську плату.

15 травня 2002 року з'являється перший процесор під назвою Celeron, побудований з урахуванням Pentium 4, з частотою 1.7 ГГц. Пізніше, 12 червня 2002 з'являється версія на 1.8 ГГц.

Новий Celeron, як і раніше, використовує 100 МГц системну шину, щоправда, тепер уже з передачею 4-х сигналів за такт. Вчорашня 100 МГц системна шина вирішує стару проблему Celeron - недолік пропускної спроможності FSB.

Як і Pentium 4 Willamette, новий Celeron виконаний із застосуванням 0.18 мкм. техпроцесу. Складається із 42 млн. транзисторів. Випускається із частотами 1.7 та 1.8 ГГц.

Наступне та останнє на сьогоднішній день ядро процесора Celeron, це Northwood(Звичайно з урізаним до 128 Кб кешем другого рівня). Першим процесором у цьому ядрі був Celeron 2.0 ГГц, який вийшов 18 вересня 2002 року. Він, як і Celeron Willamette 128, повністю повторює характеристики старшого брата Pentium 4 Northwood, за винятком шини розрахованої виключно на 400 МГц (4*100 МГц) та кешу другого рівня розміром 128 Кб.

Застосування: 0.13 мкм. техпроцесу дає перевагу у вигляді гарної розганяльності. Ядро Northwood має хороший частотний потенціал (на сьогоднішній день до 3.2 ГГц), тому запас для розгону є.

З моменту першого випуску Intel Pentium II Xeon пройшло трохи менше трьох років. І Intel, 21 травня 2001 року, продовжуючи свій курс із сегментування своїх процесорів, анонсує процесор Xeon наступного покоління, який базується на ядрі Pentium 4 Willamette. Процесор називається по-старому, Intel Xeon, і випускається у трьох варіантах: 1.4 ГГц, 1.5 ГГц та 1.7 ГГц. Ядро процесора майже повністю ідентичне звичайній (desktop) версії Pentium 4 крім незначних деталей. Це означає, що новий Xeon має все те, що є в Pentium 4 як переваги нової архітектури, так і її недоліки.

Перші моделі Xeon випускалися із застосуванням 0.18 мкм. техпроцесу, з ядром, що практично повністю повторював Pentium 4 Willamette і носив кодове ім'я Foster. Процесор випускався із тактовими частотами до 2,0 ГГц. Складався із 42 млн. транзисторів.

Кеш пам'ять першого рівня, як і у всіх процесорів лінійки Pentium 4, з архітектурою NetBurst, 8 Кб кеш даних. Кеш другого рівня – 256 Кб з покращеною передачею даних (256 Кб Advanced Transfer Cache). Також як у Pentium 4 Willamette, у новому Xeon застосована 400 МГц системна шина (4*100 МГц) яка синхронно працює з двома каналами пам'яті на частоті 400 МГц.

Історично, лінійки процесорів Intel Xeon (тобто Pentium II Xeon, Pentium III Xeon) завжди використовували відмінний від звичайних версійпроцесора конструктив. У той час як процесори Pentium II і Pentium III випускалися в 242-контактному Slot1 варіанті, їх Xeon версії використовували 330-контактний роз'єм Slot-2. Більшість додаткових ніжок використовували для постачання чіпа додатковою енергією. З двома мегабайтами L2 кешу Pentium III Xeon споживав більше енергії, ніж його 256-кілобайтний побратим. Аналогічна ситуація сталася і з новим Xeon. Якщо перші процесори Pentium 4 Willamette використовують 423-контактний роз'єм, то в Xeon застосовується 603-контактний інтерфейс, призначений для використання в роз'ємі Socket 603. Процесор може працювати тільки в одно-або двопроцесорних конфігураціях.

9 січня 2002 року з'являються процесори Xeon, створені з урахуванням ядра Northwood із застосуванням 0.13 мкм. техпроцесу, та оснащені 512 Кб кеш пам'яті другого рівня. Кодова назва ядра – Prestonia. Від свого попередника - Xeon Foster, відрізняється лише збільшеним кешем та більш досконалим техпроцесом. Процесори працюють на частотах від 1.8 ГГц до 3.0 ГГц. Складаються із 55 млн. транзисторів. У процесорах із ядром Prestonia вперше з'явилася підтримка Hyper-Threading.

12 березня 2002 року, виходить процесор Xeon MP. Виготовлений із застосуванням 0.18 мкм. та оснащений 256 Кб кеш пам'яті другого рівня. Основна відмінність від процесорів Xeon Foster – можливість працювати в багатопроцесорних системах. Працюють на частотах від 1,4 до 1,6 ГГц. Також у цих процесорах здійснено підтримку технології Hyper-Threading.

4 листопада 2002 з'являються процесори Xeon MP, виготовлені із застосуванням 0.13 мкм. техпроцесу. Ці процесори, що працюють на частотах 1.5 ГГц, 1.9 ГГц і 2.0 ГГц, відрізняються від свого побратима Xeon Prestonia, не тільки можливістю роботи в багатопроцесорних конфігураціях, але і наявністю інтегрованого кеша третього рівня розміром 1 або 2 Мб. Завдяки цьому збільшилася кількість транзисторів, що становлять процесор до 108 млн.!

18 листопада 2002 року з'явилися процесори Xeon, що працюють на 533 МГц (4 * 133 МГц) системній шині. Ці процесори виготовлені на ядрі Prestonia, із застосуванням 0.13 мкм. Техпроцес і складаються з 108 млн. транзисторів. Кеш пам'ять другого рівня – 512 Кб. Кеш третього рівня 1 Мб. Процесори Xeon на 533 МГц шині випускаються з тактовими частотами від 2.0 ГГц до 3.06 ГГц (вийшов 10 березня 2003 року). Також нещодавно було анонсовано 3.2 ГГц процесор.

Наприкінці 2003 року Intel представить нове ядро для своїх процесорів. Prescott. Ці процесори виготовлятимуться із застосуванням 0.09 мкм. (90 нм) технології. Ядро Prescott складатиметься з 125 млн. транзисторів і міститиме 1 Мб кеш другого рівня. Також, можливо буде збільшено кеш першого рівня до 32 Кб. Природно, що нове ядро матиме підтримку технології Hyper-Threading. Тільки це вже буде Hyper-Threading 2, подальший розвиток"багатопроцесорності" в одному чіпі. У чому полягатиме їхня відмінність поки не відомо, але є припущення (ніким не підтверджені), що новинка дозволяє в одному фізичному процесорі бачити не два, а кілька віртуальних процесорів.

Також буде додано новий набір інструкцій (або розширений вже присутній), що включає 15 нових інструкцій з переведення чисел з плаваючою комою в цілі, арифметику комплексних чисел, спеціальні команди для декодування відео, SIMD-інструкції для формату з плаваючою комою та процес синхронізації потоків.

Перші процесори з цим ядром працюватимуть на частотах 3.2 та 3.4 ГГц. Їхні корпуси будуть сумісні з використовуваними зараз у процесорах Pentium 4 Northwood. Надалі процесори Prescott будуть переведені в нову упаковку LGA 775, що містить 775 висновків, для якої будуть потрібні нові материнські плати з роз'ємом Socket T.

На базі нового ядра буде продовжено випуск процесорів лінійки Celeron. Тільки тепер це вже зовсім не той Celeron, що раніше. Чіпи Celeron на ядрі Prescott будуть швидше за попередників на Northwood не тільки за рахунок збільшеної тактової частоти ядра. Вони підтримуватимуть системну шину з частотою 533 МГц, а їх кеша збільшиться з 128 до 256 кб. Перші Celeron на ядрі Prescott матимуть частоти 2.8 та 3.06 ГГц. Не встигнувши випустити процесори за 90-нм технології, Intel вже розвиває наступне покоління технології виробництва чіпів - з нормами 65 нм. Також ведуться розробки, і є чіпи, що працюють, виготовлені із застосуванням не тільки 0.065 мкм. техпроцесу, а й 45 нм, 32 нм і навіть 22 нм.

За Prescott піде ядро Tejasіз шиною 1066 МГц. На його основі буде представлено вісім різних процесорів з тактовими частотами від 6 до 9.2 ГГц. Поява у продажу першого з них запланована на кінець 2004 року. Після цього компанія представить ядро Nehalem, що використовує системну шину 1200 МГц і дозволяє отримати робочу частоту понад 10 ГГц Nehalem буде заснований на повністю новій архітектурі. Це буде не модернізований Pentium 4, як Prescott та Tejas. У ньому буде застосовано систему апаратного захисту LaGrande, і за деякими даними, використано більш досконалу технологію багатопотокової обробки. Число транзисторів у чіпі складе близько 150-250 мільйонів. З'явитися Pentium Nehalem мають у 2005 році.

Також нещодавно був оголошений новий процесор із лінійки Pentium 4 - Intel Pentium 4 Extreme Edition.

Він оснащений технологією Hyper-Threading, що працює на системній шині 800 МГц, має тактову частоту ядра 3.2 ГГц. Але головною його відмінністю від попередніх Pentium 4 стала наявність інтегрованої кристал кеш-пам'яті третього рівня L3 об'ємом 2 Мб! Ця кеш-пам'ять доповнює стандартний кеш L2 512 кбайт і працює також на частоті ядра процесора (правда, з набагато більшою латентністю, оскільки вона асинхронна і покликана прискорювати роботу з даними з областей, що найчастіше використовуються) системної пам'яті). Таким чином, новий Pentium 4 Extreme Edition має кеш-пам'ять об'ємом 2.5 Мб! А також є єдиним desktop процесором із кешем третього рівня, інтегрованим у ядро.

Процесор Pentium 4 Extreme Edition позиціонується Intel головним чином для ігрового ринку, хоча не виключено його застосування в продуктивних робочих станціях. Новий процесор використовує ядро від мультипроцесорних Xeon MP з інтегрованою кеш-пам'яттю L3. Його трохи змінили з метою підтримки системної шини 800 МГц, зменшення енергоспоживання та ін. та упаковали у стандартний корпус від Pentium 4.

При написанні даного матеріалу було використано інформацію з Інтернет сайтів

Олексій Гавриленко aka [-Alex-]

Pentium (вимовляється Пентіум) – торгова марка кількох поколінь мікропроцесорів сімейства x86, що випускаються корпорацією Intel з 22 березня 1993 року. Pentium є процесором Intel п'ятого покоління та прийшов на зміну Intel 80486 (який часто називають просто 486).

Відмінності від i3(4)86:

- адресна пам'ять у травленні з попередньою моделлю не змінилася;

- шана даних 64 біта (якщо Pentium 32 біта);

- вперше 2 конвеєри самостійно зчитує та обробляє потоки;

- вперше з'явилося спекулятивне виконання команд;

- вперше використовується така технологія, як автоматичне перевпорядкування команд:

Змінений порядок ні на що не впливає. АЛЕ проблема - умовний перехід.

ADD AX, BX ADD CX, AX YZ M1 MOV DX, 5h

Рішення: передбачається, що перехід виконався, отже, відбулося зчитування команди до конвеєра; якщо з'ясовується, що все правильно – продовжується виконання, інакше – відбувається скидання конвеєра та перезавантаження з місця переходу.

Підстави для припущення:

- статистика переходів (якщо багато, кратний цикл);

- блок прогнозів використовує статистику: якщо перехід умовний, вказує назад, то з великою ймовірністю виконається. (Приклад: repeat until). А якщо вперед, то велика ймовірність, що не виконуватиметься.

Вперше апаратна підтримка мультипроцесорності (з'єднання за допомогою спеціальної шини/спец інтерфейсу)

(Шина даних 32 ----> 64, так як 2 конвейєри)

Тактова частота Pentium: 60-150 МГц Тактова частота MMX: 200 МГц

Існують додаткові регістри, відповідальні за минуле початку коду число тактів.

Існує команда CPUID – ідентифікатор CPU.

Різні регістри.

Архітектурна особливість

(до цього CISC) Існує внутрішній перекодувальник перетворення CISC команд у внутрішній код RISC в оболонці CISC.

Переривання: раніше -> PIC (програмний контролер переривання).

Раніше джерело перериває сигнал на ніжці процесора, і адреса переходу.

APIC: джерело - повідомлення, яке надходить спеціальною шиною.

Процесор Intel Pentium P6200

Intel Pentium P6200- процесор початкового рівня, призначений для ноутбуків. Він працює на частоті 2.13 ГГц, але, на жаль, не підтримує технологію TurboBoost автоматичного розгону. Крім того, відсутня функція шифрування AES та підтримка багатопоточності. CPU підтримує технологію Enhanced Speedstep, яка дозволяє знизити енергоспоживання під час низького навантаження на процесор, але інші енергозберігаючі технології в цьому процесорі відключені (як і в серії Penryn Pentium).

P6200 заснований на мікроархітектурі Arrandale, отже, має вбудований контролер пам'яті та графічну карту Intel HD Graphics (обидва виготовлені по 45 нм технологічного процесу, а CPU по 32 нм). Вбудована відеокарта GMA HD працює на частоті 500 МГц та здатна розганятися до 667 МГц завдяки технології Turbo Boost.

Продуктивність даного процесора трохи обмежена через низьку тактову частоту і відсутність Turbo Boost і Hyperthreading. Якщо судити за показником частоти ГГц, то процесор Pentium P6200 повинен бути трохи краще, ніж Core 2 Duo з аналогічною тактовою частотою, через вбудований контролер пам'яті і невеликих поліпшень в ядрі.

*Вказані тактові частоти можуть бути змінені виробникомІсторія появи Pentium процесора

Одним звичайним тихим недільним ранком 10 травня 1992 року чотири інженера фірми INTEL прибули в аеропорт San Jose International. Встановивши відеоапаратуру, Анджела Чанг, Ерік Деваннайн, Автар Саїні та Сухель Заатрі нервозно походжали залою, чекаючи з хвилини на хвилину літака з Орегона.

Коли Марк Хопман, через кілька хвилин після приземлення літака, вийшов з коридору, тримаючи в руках маленьку блакитну валізу, вся група, що зустрічала, попрямувала до нього. Вся увага була прикута до валізи, в якій був продукт розробників 5 Орегонської фабрики. Важко було повірити, що в цій валізі був результат трирічної праці багатьох людей, втілений у маленький чіп. Так почалося життя Pentium процесора, який формально було представлено 22 березня 1993 року.

У той час, коли Винод Дем робив перші нариси, розпочавши у червні 1989 року розробку Pentium процесора, він і не підозрював, що саме цей продукт буде одним із головних досягнень фірми INTEL. З появою Pentium процесора ринок комп'ютерів відразу змінився і розпочався новий етап конкуренції. San Microsistems, MIPS та інші продавці RISC процесорів, які розробляють супершвидкі чіпи, беззастережно визнали, що новий процесор фірми INTEL стане стандартом нових настільних PC.

Процес народження Pentium процесора був нелегким

За теорією, створюючи процесор, команда розробників створює концепцію проекту, у якому визначаються його основні властивості та нововведення. Далі інженери проектують логіку, яка потім втілюється у конкретні схеми. Щойно закінчується схемотехнічне проектування, проектувальники топології промальовують кожен транзистор. В результаті їх праці створюється кінцевий шаблон. Реально все було інакше. Традиційний процес проектування був кардинально перероблений, оскільки були потрібні прискорені темпи реалізації проекту.

Як тільки команда розробників виконувала локальне завдання, менеджери перерозподіляли ресурси. Кожен інженер вирішував персональне завдання. Командний дух постійно зазнавав таких випробувань, як затримки та труднощі, проте тимчасовий план виконання проекту від цього не залежав. Для виконання всіх завдань використовувалися останні досягнення автоматизованого проектування. Дуже нагоді досвід, накопичений при проектуванні та вирішенні аналогічних проблем в 286, Intel386 і Intel486 процесорах.

Як тільки виконувався черговий етап проекту, одразу розпочинався процес всеосяжного тестування. Було бажання не повторити проблеми, що виникли свого часу з Intel486, які затримали його запуск у виробництво. Кожна помилка трасувалась у зворотному порядку та усувалися її причини. Інші інженери виконували сотні тестувань для перевірки логіки, архітектури та загальної конструкції. Вони виконали більш ніж 5000 уточнюючих тестувань, перш ніж Pentium процесор знайшов свою архітектуру. Для тестування було розроблено спеціальну технологію, що дозволила імітувати функціонування Pentium процесора з допомогою програмованих пристроїв, об'єднаних на 14 платах з допомогою кабелів. Тільки коли було виявлено всі помилки, процесор зміг працювати у реальній системі. На додаток до всього, у процесі розробки та тестування Pentium процесора брали активну участь усі основні розробники персональних комп'ютеріві програмного забезпеченнящо чимало сприяло загальному успіху проекту.

Наприкінці 1991 року, коли було завершено макет процесора, інженери змогли запустити у ньому програмне забезпечення. Проекувальники почали вивчати під мікроскопом розведення та проходження сигналів по підкладці з метою оптимізації топології та підвищення ефективності роботи. Проектування переважно було завершено у лютому 1992 року. Почалося всеосяжне тестування досвідченої партії процесорів, протягом якого піддавалися випробуванням всі блоки і вузли. У квітні 1992 року було прийнято рішення, що настав час починати промислове освоєння Pentium процесора. Як основна промислова база була обрана 5 Орегонська фабрика.

Понад 3 мільйони транзисторів було остаточно перенесено на шаблони. Почалося промислове освоєння виробництва та доведення технічних характеристик, що завершилися через 10 місяців, 22 березня 1993 широкою презентацією Pentium процесора.

Сучасна мікропроцесорна технологія фірми INTEL

Досягнення фірми INTEL у мистецтві проектування та виробництва напівпровідників уможливлюють виробляти потужні мікропроцесори в дедалі менших корпусах. Розробники мікропроцесорів в даний час працюють з комплементарним технологічним процесом металоксид напівпровідник (CMOS) з роздільною здатністю менше, ніж мікрон.

Використання субмікронної технології дозволяє розробникам фірми INTEL мати більше транзисторів на кожній підкладці. Це уможливило збільшення кількості транзисторів для сімейства X86 від 29,000 в 8086 процесорі до 1,2 мільйонів у процесорі Intel486 DX2, з найвищим досягненням у Pentium процесорі. Виконаний за 0.8 мікронною BiCMOS технологією, він містить 3.1 мільйона транзисторів. Технологія BiCMOS поєднує переваги двох технологій: біполярної (швидкість) та CMOS (мале енергоспоживання). За допомогою більш ніж у два рази більшої кількості транзисторів Pentium процесора в порівнянні з Intel486, розробники помістили на підкладці компоненти, що раніше розташовувалися зовні процесора. Наявність компонентів усередині зменшує час доступу, що значно збільшує продуктивність. 0.8 мікронна технологія фірми INTEL використовує тришаровий метал і має більш високий рівень порівняно з оригінальною 1.0 мікронною технологією двошарового металу, що використовується в процесорі Intel486.

Фірма INTEL використовувала останні досягнення технології проектування мікропроцесорів для досягнення переваг, порівнянних з альтернативними архітектурами, що використовуються в наукових та інженерних робочих станціях, забезпечивши при цьому сумісність із програмним забезпеченням вартістю $50 мільярдів, напрацьованого для сімейства мікропроцесорів серії X86.

Та й саме програмне забезпечення для Pentium процесора розроблялося за новою технологією. Ще на етапі проектування апаратних засобів процесора до проекту стали залучатися експерти з усіх основних компаній, що розробляють операційні системи та компілятори – Microsoft, IBM, NeXT, Borland, Watcom, MetaWare та ін. Це дозволило на апаратному рівні підтримати нові технології програмування з урахуванням фірмового стилю постачальників стандартного програмного забезпечення З іншого боку, ще до народження нового процесора використовувалися методи класичної та спеціальної оптимізації, що розкривають специфічні переваги архітектури X86, наприклад використання команд завантаження-запису, потужних режимів адресації, видалення інваріантних ділянок коду з циклів і т.д. Тепер тільки за рахунок перекомпіляції традиційних додатків вдається підвищити їхню продуктивність на новому процесорі ще вдвічі. Такого в даний час не може запропонувати не один із конкурентів фірми INTEL.

Нове покоління процесорів фірми INTEL

Об'єднуючи більш ніж 3.1 мільйон транзисторів на одній кремнієвій підкладці, 32-розрядний Pentium процесор характеризується високою продуктивністю з тактовою частотою 60 і 66 МГц. Його суперскалярна архітектура використовує вдосконалені способи проектування, які дозволяють виконувати більш ніж одну команду за один період тактової частоти, в результаті чого Pentium може виконувати величезну кількість PC-сумісного програмного забезпечення швидше, ніж будь-який інший мікропроцесор. Крім існуючих напрацювань програмного забезпечення, високопродуктивний арифметичний блок з плаваючою комою Pentium проесора забезпечує збільшення обчислювальної потужності до необхідної для використання недоступних раніше технічних та наукових додатків, спочатку призначених для платформ робочих станцій. Також, як локальні та глобальні мережі продовжують витісняти застарілі ієрархічні мережі, керовані великими ЕОМ, переваги мультипроцесорності та гнучкість операційної системи Pentium процесора – ідеал для хост-комп'ютера для сучасних додатків клієнт-серверів, що застосовуються в промисловості.

Оскільки Pentium процесор здатний досягати рівня продуктивності рівного або вищого, ніж сучасні робочі станції високого рівня, він має переваги, яких позбавлені звичайні робочі станції: повна сумісність з більш ніж 50 000 програмних додатківз вартістю мільярди доларів, написаних під ахітектуру фірми INTEL. Крім того, процесор Pentium дозволяє використовувати всі основні операційні системи, які доступні сучасним настільним персональним комп'ютерам, робочим станціям і серверам, включаючи UNIX, Windows-NT, OS/2, Solaris і NEXTstep.

Pentium процесор. Технічні нововведення

Численні нововведення - характерна особливість Pentium процесора у вигляді унікального поєднання високої продуктивності, сумісності, інтеграції даних та нарощуваності. Це включає:

- Суперскалярну архітектуру;

- Роздільне кешування програмного коду та даних;

- Блок передбачення правильної адреси переходу;

- Високопродуктивний блок обчислень з плаваючою комою;

- Розширену 64-бітову шину даних;

- Підтримка багатопроцесорного режиму роботи;

- засоби завдання розміру сторінки пам'яті;

- Засоби виявлення помилок та функціональної надмірності;

- Управління продуктивністю;

- Нарощування за допомогою Intel OverDrive процесора.

Архітектура Pentium процесора

1 – 64-бітовий шинний інтерфейс;

2 – Засоби кешування програмного коду;

3 - Буфери вибірки із випередженням;

4 - 32-бітовий цілий блок АЛУ;

5 - 32-бітовий цілий блок АЛУ;

6 - Набір регістрів;

7 - Засоби кешування даних;

8 - Блок передбачення правильної адреси переходу;

9 - Блок конвейєрних обчислень з плаваючою комою.

Суперскалярна архітектура

Суперскалярна архітектура Pentium процесора є сумісною лише з INTEL двоконвейєрною індустріальною архітектурою, що дозволяє процесору досягати нових рівнів продуктивності за допомогою виконання більш ніж однієї команди за один період тактової частоти. Термін "суперскалярна" означає мікропроцесорну архітектуру, яка містить більше одного обчислювального блоку. Ці обчислювальні блоки, або конвейєри, є вузлами, де відбуваються всі основні процеси обробки даних та команд.

Поява суперскалярної архітектури Pentium процесора є природним розвитком попереднього сімейства процесорів з 32-бітовою архітектурою фірми INTEL. Наприклад, процесор Intel486 здатний виконувати кілька своїх команд за період тактової частоти, проте попередні сімейства процесорів фірми INTEL вимагали безліч циклів тактової частоти до виконання однієї команди.

Можливість виконувати безліч команд за період тактової частоти існує завдяки тому, що Pentium процесор має два конвейєра, які можуть виконувати дві інструкції одночасно. Так само, як і Intel486 з одним конвейером, подвійний конвейєр Pentium процесора виконує просту командуза п'ять етапів: попередня підготовка, перше декодування (декодування команди), друге декодування (генерація адреси), виконання та зворотне вивантаження. Це дозволяє кільком командам перебувати у різних стадіях виконання, збільшуючи цим обчислювальну продуктивність.

Кожен конвейєр має своє арифметично-логічне пристрій (ALU), сукупність пристроїв генерації адреси та інтерфейс кешування даних. Так само як і процесор Intel486, Pentium процесор використовує апаратне виконання команд, що замінює безліч мікрокоманд, що використовуються в попередніх сімейства мікропроцесорів. Ці інструкції включають завантаження, запам'ятовування та прості операції АЛУ, які можуть виконуватися апаратними засобами процесора без використання мікрокоду. Це підвищує продуктивність без торкання сумісності. У разі більш складних команд, для додаткового прискорення продуктивності виконання розширеного мікрокоду Pentium процесора для виконання команд використовуються обидва конвейєри суперскалярної архітектури.

В результаті цих архітектурних нововведень, порівняно з попередніми мікропроцесорами, значно більша кількість команд може бути виконана за один і той самий час.

Роздільне кешування програмного коду та даних

Інше найважливіше революційне удосконалення, реалізоване в Pentium процесорі, це запровадження окремого кешування. Кешування збільшує продуктивність за допомогою активізації місця тимчасового зберігання для програмного коду, що часто використовується, і даних, що отримуються з швидкої пам'яті, замінюючи по можливості звернення до зовнішньої системної пам'яті для деяких команд. Процесор Intel486, наприклад, містить один 8-KB блок вбудованої кеш-пам'яті, яка використовується одночасно для кешування програмного коду та даних.

Проектувальники фірми INTEL обійшли це обмеження використанням додаткового контуру, виконаного на 3.1 мільйонах транзисторів Pentium процесора (для порівняння, Intel486 містить 1.2 мільйони транзисторів), що створюють роздільне внутрішнє кешування програмного коду та даних. Це покращує продуктивність за допомогою виключення конфліктів на шині та робить подвійне кешування доступним частіше, ніж це було можливо раніше. Наприклад, під час фази попередньої підготовкивикористовується код команди, отриманий з кешу команд. У разі наявності одного блоку кеш-пам'яті, можливий конфлікт між процесом попередньої підготовки команди та доступом до даних. Виконання роздільного кешування для команд та даних виключає такі конфлікти, даючи можливість обом командам виконуватися одночасно. Кеш-пам'ять програмного коду та даних Pentium процесора містить по 8 KB інформації кожна, і кожна організована як набір двоканального асоціативного кеша - призначена для запису лише попередньо переглянутого специфікованого 32-байтного сегмента, причому швидше ніж зовнішній кеш. Всі ці особливості розширення продуктивності зажадали використання 64-бітової внутрішньої шини даних, яка забезпечує можливість подвійного кешування та суперскалярної обробки конвеєрної одночасно з завантаженням наступних даних. Кеш даних має два інтерфейси, по одному для кожного конвеєра, що дозволяє йому забезпечувати даними дві окремі інструкції протягом одного машинного циклу. Після того, як дані дістаються з кешу, вони записуються в головну пам'ять як зворотний запис. Така техніка кешування дає кращу продуктивність, Чим просте кешування з безпосереднім записом, при якому процесор записує дані одночасно в кеш та основну пам'ять. Тим не менш, Pentium процесор здатний динамічно конфігуруватися для підтримки кешування з безпосереднім записом.

Таким чином, кешування даних використовує два різні чудові рішення: кеш зі зворотним записом і алгоритм, названий MESI (модифікація, виключення, розподіл, звільнення) протокол. Кеш із зворотним записом дозволяє записувати в кеш без звернення до основної пам'яті на відміну від використовуваного до цього безпосереднього простого кешування.

Ці рішення збільшують продуктивність за допомогою використання перетвореної шини і запобіжного виключення найвужчого місця в системі. У свою чергу MESI-протокол дозволяє даними в кеш-пам'яті та зовнішньої пам'ятізбігатися - чудове рішення у вдосконалених мультипроцесорних системах, де різні процесори можуть використовувати до роботи одні й самі дані.

Високопродуктивний блок обчислень з плаваючою комою

Наростаюча хвиля 32-розрядних програмних додатків включає багато інтенсивно обчислювальних, графічно орієнтиро-програм, які займають багато процесорних ресурсів на виконання операцій з плаваючою комою, що забезпечують математичні обчислення. Оскільки вимоги до персональних комп'ютерів з боку програмного забезпечення з обчислення з плаваючою комою постійно зростають, задовольнити ці потреби можуть удосконалення мікропроцесорної технології. Процесор Intel486 DX, наприклад, був першим мікропроцесором, інтегрованим на одній підкладці з математичним співпроцесором. Попередні сімейства процесорів фірми INTEL, за потреби використання обчислень з плаваючою комою, використовували зовнішній математичний співпроцесор.

Pentium процесор дозволяє виконувати математичні обчислення на вищому рівні завдяки використанню удосконаленого вбудованого блоку обчислень з плаваючою комою, що включає восьмитактовий конвейєр та апаратно реалізовані основні математичні функції. Чотиритактові конвейєрні команди обчислень з плаваючою комою доповнюють чотиритактову цілочисленну конвеєризацію. Більшість команд обчислень з плаваючою комою можуть виконуватися в одному цілісному конвейєрі, після чого подаються в конвейєр обчислень з плаваючою комою. Звичайні функції обчислень з плаваючою комою, такі як додавання, множення та поділ, реалізовані апаратно з метою прискорення обчислень.

В результаті цих інновацій Pentium процесор виконує команди обчислень з плаваючою комою в п'ять разів швидше, ніж 33-МГц Intel486 DX, оптимізуючи їх для високошвидкісних чисельних обчислень, що є невід'ємною частиною таких удосконалених відеододатків, як CAD і 3D-графіка.

Pentium процесор на тактовій частоті 66 МГц працює як "числодробилка" з рейтингом 64.5 за тестом SPECint92, практично не поступаючись RISC-процесору Alpha компанії Digital, але з тактовою частотою вдвічі вищою.

Загальна продуктивність Pentium процесора перевищує 6 разів 25 МГц Intel486 SX й у 2.6 разів - 66 МГц Intel486 DX2. Індекс рейтингу iCOMP для 66 МГц Pentium процесора, який виконує 112 мільйонів операцій на секунду, становить 567. Індекс iCOMP (Intel COmparative Microprocessor Peformance) виконує відносне порівняння продуктивності 32-бітових процесорів фірми INTEL.

Розширена 64-бітова шина даних

Pentium процесор зовні є 32-бітовий пристрій. Зовнішня шина даних до пам'яті є 64-бітовою, подвоюючи кількість даних, що передаються протягом одного шинного циклу. Pentium процесор підтримує кілька типів шинних циклів, включаючи пакетний режим, протягом якого відбувається порція даних з 256 біт кеш даних і протягом одного шинного циклу.

Шина даних є головною магістраллю, яка передає інформацію між процесором та підсистемою пам'яті. Завдяки цій 64-бітовій шині даних, Pentium процесор суттєво підвищує швидкість передачі порівняно з процесором Intel486 DX – 528 MB/сек для 66 МГц, порівняно зі 160 MB/сек для 50 МГц процесора Intel486 DX. Ця розширена шина даних сприяє високошвидкісним обчисленням завдяки підтримці одночасного підживлення командами та даними процесорного блоку суперскалярних обчислень, завдяки чому досягається ще більша загальна продуктивність Pentium процесора порівняно з процесором Intel486 DX.

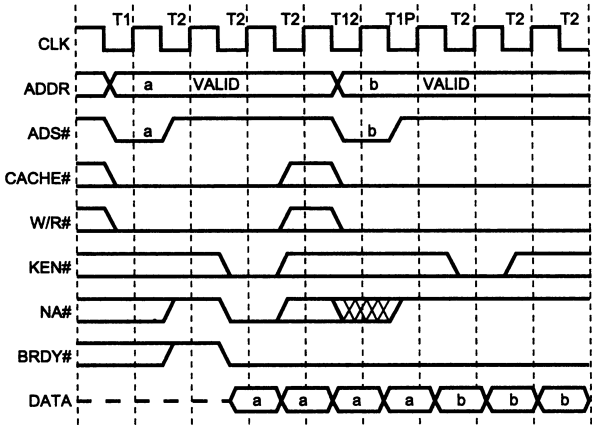

Загалом, маючи ширшу шину даних, Pentium процесор забезпечує конвеєризацію шинних циклів, що сприяє збільшенню пропускної спроможності шини. Конвеєризація шинних циклів дозволяє другому циклу стартувати раніше завершення виконання першого циклу. Це дає підсистемі пам'яті більше часу для декодування адреси, що дозволяє використовувати повільніші та менш дорогі компоненти пам'яті, зменшуючи в результаті загальну вартість системи. Прискорення процесів читання та запису, паралелізм адреси та даних, а також декодування протягом одного циклу – все разом дозволяє покращити пропускну здатність та підвищує можливості системи.

Мультипроцесорність

Pentium процесор - це ідеал для наростаючої хвилі мультипроцесорних систем, а також найвищий рівень продуктивності та обчислювальної потужності в галузі сучасних обчислювальних засобів. Мультипроцесорні додатки, які з'єднують два або більше Pentium процесорів - добре обслуговуються за допомогою вдосконаленої архітектури кристалів, окремим вбудованим кешуванням програмного коду та даних, а також наборами мікросхем для керування зовнішньою кеш-пам'яттю та витонченими засобами контролю цілісності даних.

Як раніше обговорювалося, Pentium процесор підтримує впорядкований кеш з його MESI протоколом. Коли один процесор отримує доступ до даних, які кешуються в іншому процесорі, він може приймати правильні дані. І якщо дані модифікувалися, всі процесори отримують можливість доступу до прийому даних модифікованому вигляді. Новий Pentium процесор фірми INTEL також визначає, які команди розпізнаються системою відповідно до способу програмування, що використовується. Це суворо точно підказує, яким чином програмному забезпеченню, розробленому для однопроцесорної системи, коректно працювати в багатопроцесорному оточенні.

Засоби поділу пам'яті на сторінки

Pentium процесор пропонує опції підтримки будь-якої з традиційних розмірів сторінок пам'яті – 4 KB або ширші, 4 MB сторінки. Ця опція дозволяє проводити обчислення частоти свопінгу сторінок у комплексних графічних додатках, буферах кадрів, а також ядер операційних систем, де збільшений розмір сторінки зараз дозволяє користувачам перепланувати ширше спочатку громіздкі об'єкти. Збільшення сторінок дає результат у вигляді підвищення продуктивності, причому все це відбивається на прикладному програмному забезпеченні.

Визначення помилок та функціональна надмірність

Хороший захист даних та забезпечення їх цілісності за допомогою внутрішніх засобів стає вкрай важливим у додатках, критичним до втрат даних завдяки поширенню сучасного оточення клієнт-серверів. Pentium процесор містить два вдосконалення, традиційно властиві проектування класу великих ЕОМ - внутрішнє визначення помилок і контроль за рахунок функціональної надмірності (FCR) - це допомагає забезпечити цілісність даних систем, що розвиваються сьогодні, базуються на настільних комп'ютерах.

Внутрішнє визначення помилок доповнює бітом парності внутрішній код і кешування даних, асоціативну зсувну таблицю сторінок, мікрокод, а також цільовий буфер переходу, допомагаючи визначати помилки таким чином, що це залишається непомітним і для користувача, і для системи. У той же час контроль за допомогою функціональної надмірності оптимізований для додатків, критичних до втрат даних, де процесор Pentium може працювати в конфігурації основний/контролюючий. Якщо між двома процесорами виявляються розбіжності, система повідомляється про помилку. В результаті відбувається виявлення більш ніж 99% помилок.

Крім того, на підкладці процесора розташований пристрій вбудованого тестування. Самотестування охоплює більше 70% вузлів Pentium процесора, не вимагає виконання скидання кристала і є процедурою, що зазвичай використовується при діагностиці систем. Іншими вбудованими рішеннями є реалізація стандарту IEEE 1149.1, що дозволяє тестувати зовнішні з'єднання проесора та налагоджувальний режим, що дозволяє програмному забезпеченню переглядати регістри та стан процесора.

Управління продуктивністю

Управління продуктивністю - особливість Pentium процесора, що дозволяє розробникам систем та прикладних розширень оптимізувати свої апаратні та програмні засобиза допомогою визначення потенційно вузького місця для програмного коду. а робітники можуть спостерігати та вважати такти для внутрішніх подій процесора, таких, як продуктивність читання та запису даних, кешування збігів та випадень, переривань та використання шини. Це дозволяє їм вимірювати ефективність, яку має код у подвійній архітектурі Pentium процесора та у своїх продуктах та виконувати тонке налаштування своїх додатків чи систем для досягнення оптимальної продуктивності. Вигода для кінцевих користувачів - це вищі переваги та вища продуктивність, і все це завдяки гарній взаємодії з Pentium процесором, системою користувача і прикладним програмним забезпеченням.

Даючи можливість розробникам проектувати системи з керуванням енергоспоживанням, захистом та іншими властивостями, Pentium процесор підтримуємо режим керування системою (SMM), подібний до режиму архітектури Intel SL.

Нарощування

Разом з усім, що зроблено нового для 32-бітової мікропроцесорної архітектури фірми INTEL, процесор Pentium сконструйований для легкої нарощуваності з використанням архітектури нарощування фірми INTEL. Ці нововведення захищають інвестиції користувачів за допомогою нарощування продуктивності, яка допомагає підтримувати рівень продуктивності систем, заснованих на архітектурі процесорів фірми INTEL, більша, ніж тривалість життя окремих компонентів. Технологія нарощування уможливлює використання переваг більшості процесорів удосконаленої технології у вже існуючих системах за допомогою простої інсталяції засобу однокристального нарощування продуктивності. Наприклад, перше засіб нарощування - це OverDrive процесор, розроблений для процесорів Intel486 SX та Intel486 DX, що використовує технологію простого подвоєння тактової частоти, використану під час розробки мікропроцесорів Intel486 DX2.

За допомогою нарощування одного з цих додаткових процесорів у сокет, розташований біля центрального мікропроцесора на більшості материнських плат Intel486, користувачі можуть збільшити загальну продуктивність системи більш, ніж на 70% практично для всіх програмних додатків.

Технологія нарощування за допомогою OverDrive процесорів можлива і для систем, заснованих на сімействі Pentium процесора за допомогою простої установки в майбутньому процесора, виконаного за вдосконаленою технологією. У свою чергу, технологія Pentium процесора є основою додаткового процесора, що розробляється для систем, що базуються на Intel486 DX2

Процесори Pentium фірми Intel являють собою п'яте покоління процесорів сімейства х86. За базовою реєстровою архітектурою та системою команд вони сумісні з вищеописаними 32-бітними процесорами, але мають 64-бітну шину даних, завдяки чому їх іноді помилково називають 64-розрядними. Порівняно з попередніми поколіннями процесори Pentium мають такі якісні відмінності:

- Суперскалярна архітектура: процесор має два паралельно працюючі конвеєри обробки (U-конвеєр з повним наборомінструкцій та V-конвеєр з дещо обмеженим набором), завдяки чому він здатний одночасно виконувати дві інструкції. Проте переваги цієї архітектури повністю реалізуються лише за спеціальному режимі компіляції ПЗ.

- Застосування технології динамічного передбачення розгалужень спільно з виділеним внутрішнім кешем команд обсягом 8 Кбайт забезпечує максимальне завантаження конвеєрів.

- Внутрішній (Level 1) кеш даних об'ємом до Кбайт, на відміну від 486-го, працює з відкладеним (до звільнення зовнішньої шини) записом і налаштовується на режим наскрізного або зворотного запису, підтримуючи протокол

- Зовнішня шина даних для підвищення продуктивності має розрядність 64 біт, що вимагає відповідної організації пам'яті.

- Вбудований співпроцесор за рахунок архітектурних поліпшень (конвеєризації) у 2-10 разів перевищує FPU-486 за продуктивністю.

- Введено кілька нових інструкцій, у тому числі розпізнавання сімейства та моделі CPU.

- Застосовано виявлення помилок внутрішніх пристроїв (внутрішній контроль паритету) та зовнішнього інтерфейсу шини, контролюється паритет шини адреси.

- Введено можливість побудови функціонально-надлишкової двопроцесорної системи.

- Реалізовано інтерфейс побудови двопроцесорних систем із симетричною архітектурою (починаючи з другого покоління Pentium).

- Запроваджено засоби управління енергоспоживанням.

- Застосовано конвеєрну адресацію шинних циклів.

- Скорочено час (кількість тактів) виконання інструкцій.

- Введено трасування інструкцій та моніторинг продуктивності.

- Розширено можливості віртуального режиму – введено віртуалізацію прапора переривань.

- Введено можливість оперування сторінками розміром 4 Мб у режимі переадресації сторінок (Paging).

Всі Pentium-процесори мають засоби SMM, можливості яких розширювалися з появою нових моделей. Засоби тестування включають можливість виконання вбудованого тесту BIST (Built-In Self Test), який забезпечує виявлення помилок мікрокодів, програмованих логічних матриць, тестування командної кеш-пам'яті, кеш-пам'яті зберігання даних, буфера швидкої переадресації та ROM. Усі процесори мають стандартний тестовий порт IEEE 1149.1, що дозволяє тестувати процесор за допомогою інтерфейсу JTAG.

У процесорах реалізовано нові додаткові засоби налагодження:

- зондовий режим (Probe Mode), що забезпечує доступ до внутрішніх регістрів та просторів введення-виведення системної пам'яті процесора Pentium. Цей режим дозволяє перевіряти та змінювати стан CPU, забезпечуючи засоби для налагодження програм з можливостями, подібними до внутрішньосхемних емуляторів;

- розширення налагодження DE (Debug Extensions), що дозволяють ставити контрольні точки за адресами вводу-виводу;

- внутрішні лічильники, що використовуються для поточного контролю продуктивності та обліку числа подій;

- покрокове виконання за допомогою команди CPUID.

Процесори Pentium першого покоління (Р5) з тактовою частотою 60 і 66 МГц мали напругу живлення 5, що призводило до великого тепловиділення (на частоті 66 МГц - 16 Вт). Вони випускалися у корпусах PGA-273 (матриця 21x21), для встановлення цих процесорів призначений сокет 4.