Prozessorfamilie Intel Pentium

- P54CS

- Tillamook

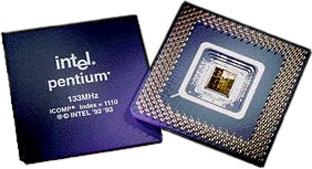

Pentium(ausgesprochen Pentium) - Warenzeichen mehrere Generationen von Mikroprozessoren der x86-Familie, hergestellt von der Intel Corporation seit dem 22. März 1993. Der Pentium ist Intels Prozessor der fünften Generation und ersetzt den Intel 80486 (oft einfach als 486 bezeichnet).

Geschichte

Modelle

Zunächst (22. März 1993) wurden nur zwei Modelle vorgestellt, die auf dem P5-Kern mit Frequenzen von 60 und 66 MHz basierten. Später kamen leistungsstärkere Pentium-Prozessoren auf den Markt, die auf verbesserten Kernen basierten. Darüber hinaus wurden mobile Versionen von Prozessoren und Pentium OverDrive-Prozessoren vorgestellt.

| Kernel-Codename | P5 | P54C | P54CS | P55C | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Technischer Prozess, nm | 800 | 600 | 350 | ||||||||||

| Kerntaktfrequenz, MHz | 60 | 66 | 75 | 90 | 100 | 120 | 133 | 150 | 166 | 200 | 166 | 200 | 233 |

| Angekündigt | 23. März 1993 | 10. Oktober 1993 | 7. März 1994 | 27. März 1995 | 12. Juni 1995 | 4. Januar 1996 | 10. Juni 1996 | 8. Januar 1997 | 2. Juni 1997 | ||||

P5

Die einzigen beiden Modelle der Pentium-Prozessoren der ersten Generation mit Kerntaktraten von 60 und 66 MHz wurden am 23. März 1993 angekündigt.

Der Prozessor wurde in einem 273-Pin-CPGA-Gehäuse hergestellt, auf dem Motherboard im Sockel 4-Prozessorsockel installiert und benötigte eine 5-V-Stromversorgung. Die Systembusfrequenz (FSB) entsprach der Kernfrequenz, also dem Kern Der Multiplikator betrug 1,0.

Alle Pentium-Prozessoren gehören zur SL Enhanced-Klasse – das bedeutet, dass sie über ein SMM-System verfügen, das den Stromverbrauch senkt. Der Second-Level-Cache befand sich auf der Hauptplatine und konnte bis zu 1 MB groß sein. Frühe Versionen von Prozessoren mit Frequenzen von 60–100 MHz (P5- und P54C-Kerne) hatten einen Fehler im mathematischen Coprozessormodul, der in seltenen Fällen zu einer Verschlechterung der Genauigkeit der Divisionsoperation führte. Dieser Fehler wurde 1994 entdeckt und als „Pentium FDIV-Bug“ bekannt.

Prozessoren auf Basis des P5-Kerns wurden in einer 800-Nanometer-Prozesstechnologie mit bipolarer BiCMOS-Technologie hergestellt. Der Prozessor enthält 3,1 Millionen Transistoren und die Kernchipgröße beträgt 294 mm². Der Pentium 66 verbraucht einen Strom von 3,2 A und hat eine Leistung von 16 W, was den Einbau eines zusätzlichen Lüfters erforderte. Die Herstellung solcher Prozessoren erwies sich als sehr schwierig und der Anteil an verwendbaren Kristallen erwies sich als zu gering. Viele Experten rieten angesichts der zahlreichen Mängel (siehe: F0 0f c7 c8) der Pentium-Prozessoren der ersten Generation vom Kauf dieser Modelle ab. Die Produktion musste vorübergehend eingestellt werden. Bald begann jedoch die Produktion verbesserter Prozessoren auf Basis des P54C-Kerns.

P54C

Die Pentium-Prozessoren der zweiten Generation nutzen Taktmultiplikation und sind schneller als der Systembus. Ein Multiplikator wird verwendet, um anzugeben, wie oft die Taktfrequenz des Prozessorkerns größer als die Systembusfrequenz ist. Bei allen Prozessoren, die auf dem P54C-Kern basieren, beträgt der Multiplikator 1,5.

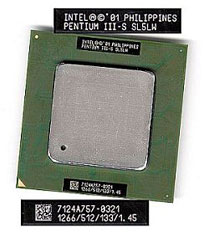

P54CS

Die ersten auf diesem Kern basierenden Prozessoren wurden am 27. März 1995 veröffentlicht. Im Wesentlichen handelt es sich bei diesem Kern um einen P54C-Kern, der mit der 350-nm-Bipolar-BiCMOS-Technologie hergestellt wurde, was es ermöglichte, die Größe des Kernchips auf 91 mm² (Pentium 120- und 133-Prozessoren) zu reduzieren, aber aufgrund der Kernoptimierung bald seine Größe wurde bei gleicher Transistoranzahl auf bis zu 83 mm² reduziert. Gleichzeitig verbrauchte der Pentium 200 einen Strom von 4,6 A und seine maximale Energieabgabe (Wärmeabgabe) betrug 15,5 W.

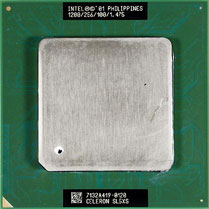

P55C

Am 8. Januar 1997 wurden Pentium-Prozessoren auf Basis des P5-Kerns der dritten Generation (P55C) veröffentlicht. Das Intel R&D Center in Haifa (Israel) hat dem P55C-Kern einen neuen Befehlssatz namens MMX (MultiMedia eXtension) hinzugefügt, der die Computerleistung bei Multimedia-Anwendungen deutlich steigert (von 10 bis 60 %, je nach Optimierung). Aus diesem Grund werden diese Prozessoren Pentium mit MMX-Technologie genannt (normalerweise abgekürzt als Pentium MMX). Der neue Prozessor enthält ein MMX-Gerät mit Pipeline-Befehlsverarbeitung, der L1-Cache wird auf 32 KB erhöht (16 KB für Daten und 16 KB für Anweisungen). Besteht aus neuer Prozessor aus 4,5 Millionen Transistoren und wird in fortschrittlicher 280-Nanometer-CMOS-Technologie unter Verwendung von Siliziumhalbleitern hergestellt, arbeitet mit einer Spannung von 2,8 V. Die maximale Stromaufnahme beträgt 6,5 A, die Wärmeableitung beträgt 17 W (für Pentium 233 MMX). Die Kristallfläche von Pentium MMX-Prozessoren beträgt 141 mm². Die Prozessoren wurden in einem 296-Pin-CPGA- oder PPGA-Gehäuse für Sockel 7 produziert.

Pentium OverDrive

Es wurden mehrere Generationen des Pentium OverDrive veröffentlicht.

- 1995 wurde der erste Pentium OverDrive veröffentlicht (auf dem P24T-Kern). Es war für den Einbau in Sockel 2 oder Sockel 3 konzipiert und arbeitete mit einer Versorgungsspannung von 5 V, d. h. es diente zur Aufrüstung von Systemen mit 486-Prozessor ohne Austausch des Motherboards. Darüber hinaus verfügte dieser Prozessor über alle Funktionen Pentium-Prozessor erste Generation (auf P5-Kern). Es wurden zwei Modelle herausgebracht, die mit Frequenzen von 63 und 83 MHz arbeiteten, das ältere verbrauchte einen Strom von 2,8 A und hatte eine Verlustleistung von 14 W. Aufgrund der hohen Kosten wurde dieser Prozessor vor seinem Erscheinen aufgegeben. Und obwohl diese Prozessoren nach einiger Zeit (4. März 1996) durch Pentium ODP5V mit Frequenzen von 120 und 133 MHz ersetzt wurden, basierend auf dem P5T-Kern (im Wesentlichen ein P54CS-Kern), erlangten sie auch keine Popularität.

- Am 4. März 1996 wurde die nächste Version von Pentium OverDrive veröffentlicht – Pentium ODP3V – basierend auf dem P54CT-Kern. Dieser Kern basiert auf dem P54CS-Kern. Der Prozessor wurde in einem 320-Pin-CPGA-Gehäuse für Sockel 5 oder Sockel 7 produziert.

- Am 3. März 1997 wurden zwei Pentium ODPMT-Modelle (mit Frequenzen von 150 und 166 MHz) veröffentlicht, die auf dem P54CTB-Kern (analog zum P55C) basieren. Später, am 4. August 1997, wurden zwei weitere Modelle auf demselben Kern (mit Frequenzen von 180 und 200 MHz) veröffentlicht. Sie wurden in 320-Pin-CPGA-Gehäusen hergestellt und waren für Sockel 5 oder Sockel 7 (Pentium ODPMT-200 MMX – nur Sockel 7) konzipiert.

Tillamook

Auf diesem Kern basierende Prozessoren waren für Laptop-Computer gedacht und wurden in den sogenannten verwendet. „mobiles Modul“ MMC-1 Mobilmodul-Anschluss mit 280 zusammengearbeiteten Pins Intel-Chipsatz 430 TX und 512 KB Cache-Speicher auf dem Motherboard. Der Tillamook-Kern (benannt nach einer Stadt in Oregon, USA) ist ein P55C-Kern mit niedrigerer Spannung – das 300-MHz-Modell arbeitete mit 2,0 V, verbrauchte 4,5 A und verbrauchte 8,4 W. Ältere Modelle (mit einer Frequenz von 233, 266 und 300 MHz) wurden in einer 250-nm-Prozesstechnologie hergestellt und hatten eine Kristallfläche von 90 mm²; es gab auch Versionen mit einer Kernfrequenz von 166 MHz. Es wurden die Modelle 200 und 233 hergestellt ab August 1997, Modell 266 ab Januar 1998, und das Spitzenmodell der Linie wurde im Januar 1999 eingeführt.

(oft einfach 486 genannt).

Enzyklopädisches YouTube

1 / 4

Warum gab es Pentium 2 auf Karten? | Nostalgie-Nerd

Pentium vs. 486 PC (1993)

Bewaffnet und entwaffnet von einer Pentium 4-CPU, praktische Übung für einen Informatikstudenten.

Warum Pentium 486 in den Arsch tritt (Pipelines & Cache) | Nostalgie-Nerd

Untertitel

Geschichte

Prozessoren auf Basis des P5-Kerns wurden in einer 800-Nanometer-Prozesstechnologie mit bipolarer BiCMOS-Technologie hergestellt. Der Prozessor enthält 3,1 Millionen Transistoren und die Kernchipgröße beträgt 294 mm². Der Pentium 66 verbraucht einen Strom von 3,2 A und hat eine Leistung von 16 W, was den Einbau eines zusätzlichen Lüfters erforderte. Die Herstellung solcher Prozessoren erwies sich als sehr schwierig und der Anteil an verwendbaren Kristallen erwies sich als zu gering. Viele Experten wiesen auf die zahlreichen Mängel (siehe: F0 0f c7 c8) der Pentium-Prozessoren der ersten Generation hin und rieten vom Kauf dieser Modelle ab. Die Produktion musste vorübergehend eingestellt werden. Bald begann jedoch die Produktion verbesserter Prozessoren auf Basis des P54C-Kerns.

P54C

Die Pentium-Prozessoren der zweiten Generation nutzen Taktmultiplikation und sind schneller als der Systembus. Ein Multiplikator wird verwendet, um anzugeben, wie oft die Taktfrequenz des Prozessorkerns größer als die Systembusfrequenz ist. Bei allen Prozessoren, die auf dem P54C-Kern basieren, beträgt der Multiplikator 1,5.

P54CS

Die ersten auf diesem Kern basierenden Prozessoren wurden am 27. März 1995 veröffentlicht. Im Wesentlichen handelt es sich bei diesem Kern um einen P54C-Kern, der mit der 350-nm-Bipolar-BiCMOS-Technologie hergestellt wurde, was es ermöglichte, die Größe des Kernchips auf 91 mm² (Pentium 120- und 133-Prozessoren) zu reduzieren, aber aufgrund der Kernoptimierung bald seine Größe wurde bei gleicher Transistoranzahl auf bis zu 83 mm² reduziert. Gleichzeitig verbrauchte der Pentium 200 einen Strom von 4,6 A und seine maximale Energieabgabe (Wärmeabgabe) betrug 15,5 W.

P55C

Am 8. Januar 1997 wurden Pentium-Prozessoren auf Basis des P5-Kerns der dritten Generation (P55C) veröffentlicht. Das Intel R&D Center in Haifa (Israel) hat dem P55C-Kern einen neuen Befehlssatz namens MMX (MultiMedia eXtension) hinzugefügt, der die Computerleistung bei Multimedia-Anwendungen deutlich steigert (von 10 bis 60 %, je nach Optimierung). Aus diesem Grund werden diese Prozessoren als Pentium mit MMX-Technologie bezeichnet (normalerweise abgekürzt als Pentium MMX). Der neue Prozessor enthält ein MMX-Gerät mit Pipeline-Befehlsverarbeitung, der L1-Cache wird auf 32 KB erhöht (16 KB für Daten und 16 KB für Anweisungen). Der neue Prozessor besteht aus 4,5 Millionen Transistoren und wird in fortschrittlicher 280-Nanometer-CMOS-Technologie unter Verwendung von Siliziumhalbleitern hergestellt, arbeitet mit einer Spannung von 2,8 V. Die maximale Stromaufnahme beträgt 6,5 A, die Wärmeableitung beträgt 17 W (für Pentium 233 MMX). Die Kristallfläche von Pentium MMX-Prozessoren beträgt 141 mm². Die Prozessoren wurden in einem 296-Pin-CPGA- oder PPGA-Gehäuse für Sockel 7 produziert.

Pentium OverDrive

Es wurden mehrere Generationen des Pentium OverDrive veröffentlicht.

- 1995 wurde der erste Pentium OverDrive veröffentlicht (auf dem P24T-Kern). Es war für den Einbau in Sockel des Typs Socket 2 oder Socket 3 konzipiert und arbeitete mit einer Versorgungsspannung von 5 V, d. h. es wurde für die Aufrüstung von Systemen mit dem 486-Prozessor ohne Austausch des Motherboards verwendet. Darüber hinaus verfügte dieser Prozessor über alle Funktionen des Pentium-Prozessors der ersten Generation (auf dem P5-Kern). Es wurden zwei Modelle herausgebracht, die mit Frequenzen von 63 und 83 MHz arbeiteten, das ältere verbrauchte einen Strom von 2,8 A und hatte eine Verlustleistung von 14 W. Aufgrund der hohen Kosten wurde dieser Prozessor vor seinem Erscheinen aufgegeben. Und obwohl diese Prozessoren nach einiger Zeit (4. März 1996) durch Pentium ODP5V mit Frequenzen von 120 und 133 MHz ersetzt wurden, basierend auf dem P5T-Kern (im Wesentlichen ein P54CS-Kern), erlangten sie auch keine Popularität.

- Am 4. März 1996 wurde die nächste Version von Pentium OverDrive veröffentlicht – Pentium ODP3V – basierend auf dem P54CT-Kern. Dieser Kern basiert auf dem P54CS-Kern. Der Prozessor wurde in einem 320-Pin-CPGA-Gehäuse für Sockel 5 oder Sockel 7 produziert.

- Am 3. März 1997 wurden zwei Pentium ODPMT-Modelle (mit Frequenzen von 150 und 166 MHz) auf den Markt gebracht, die auf dem P54CTB-Kern (analog zum P55C) basieren. Später, am 4. August 1997, wurden zwei weitere Modelle auf demselben Kern (mit Frequenzen von 180 und 200 MHz) veröffentlicht. Sie wurden in 320-Pin-CPGA-Gehäusen hergestellt und waren für Sockel 5 oder Sockel 7 (Pentium ODPMT-200 MMX – nur Sockel 7) konzipiert.

Tillamook

Auf diesem Kern basierende Prozessoren waren für Laptop-Computer gedacht und wurden in den sogenannten verwendet. Der „Mobile Module“ MMC-1 Mobile Module Connector mit 280 Pins arbeitete mit dem Intel 430 TX Chipsatz zusammen und verfügte über 512 KB Cache-Speicher auf dem Motherboard. Der Tillamook-Kern (benannt nach einer Stadt in Oregon, USA) ist ein P55C-Kern mit niedrigerer Spannung – das 300-MHz-Modell arbeitete mit 2,0 V, verbrauchte 4,5 A und verbrauchte 8,4 W. Ältere Modelle (mit einer Frequenz von 233, 266 und 300 MHz) wurden in einer 250-nm-Prozesstechnologie hergestellt und hatten eine Kristallfläche von 90 mm²; es gab auch Versionen mit einer Kernfrequenz von 166 MHz. Es wurden die Modelle 200 und 233 hergestellt ab August 1997, Modell 266 ab Januar 1998, und das Spitzenmodell der Linie wurde im Januar 1999 eingeführt.

In etwas mehr als 10 Jahren ihres Bestehens haben die Pentium-Prozessoren von Intel einen langen Weg zurückgelegt. Allein die Taktfrequenz hat sich um mehr als das 53-fache erhöht, von 60 MHz auf 3200 MHz. Intel ist auch der Autor vieler Entwicklungen, die später von Unternehmen wie AMD und VIA genutzt wurden.

In nur diesen 10 Jahren wurden die folgenden Prozessorfamilien veröffentlicht:

- 1993 – Intel Pentium

- 1995 – Intel Pentium PRO

- 1997 – Intel Pentium MMX

- 1997 – Intel Pentium II

- 1999 – Intel Pentium!!!

- 2000 – Intel Pentium 4

Schauen wir uns nun jeden von ihnen genauer an.

Alles begann am 22. März 1993. Damals stellte Intel die ersten Prozessoren unter dieser Marke vor Pentium, das viele Jahre lang zum Synonym für das Textverarbeitungsprogramm wurde.

Es war der erste Prozessor mit einer Dual-Pipe-Struktur. Hatte einen Codenamen P5. Hatte Taktraten 60 und 66 MHz. Die Busfrequenz stimmte mit der Prozessortaktfrequenz überein. Die Prozessoren enthielten mehr als 3,1 Millionen Transistoren und wurden mit der 0,80-Mikrometer-Technologie und später mit 0,60-Mikrometer-Technologie hergestellt. Die Größe des L1-Cache der ersten Ebene betrug 16 KB – 8 KB für Daten und 8 KB für Anweisungen, während sich der Cache der zweiten Ebene auf dem Motherboard befand und ein Volumen von bis zu 1 MB haben konnte. Der Prozessor wurde für den Sockel 4-Anschluss hergestellt.

Ein Jahr später, im März 1994, veröffentlichte Intel den Pentium der zweiten Generation (Core). P54).

Der Prozessor hatte Frequenzen von 75 bis 200 MHz. Busfrequenz 50-66 MHz. Die L1-Cache-Größe bleibt gleich – 16 KB (8 KB für Daten und 8 KB für Anweisungen). Der Second-Level-Cache blieb auf dem Motherboard und konnte ein Volumen von bis zu 1 MB haben. Bei der Herstellung dieses Prozessors verwendet Intel eine fortschrittlichere 0,50-Mikron-Prozesstechnologie. Der Prozessor enthielt mehr als 3,3 Millionen Transistoren. Produziert für Sockel 5, später Sockel 7.

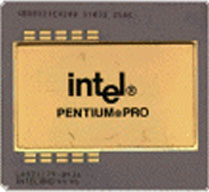

Pentium PRO

1. November 1995, mit der Veröffentlichung des Pentium PRO-Prozessors (Codename P6) hat der Countdown zur sechsten Prozessorgeneration begonnen. Sie unterschieden sich von der Vorgängergeneration durch den Einsatz dynamischer Ausführungstechnologie – Änderungen in der Reihenfolge der Befehlsausführung und der Architektur eines doppelten unabhängigen Busses. Es wurde ein weiterer Bus hinzugefügt, der den Prozessor mit dem Second-Level-Cache verbindet, der im Kern integriert ist. Dadurch wurde erstmals der L2-Cache genutzt, der mit der Prozessorfrequenz arbeitete. Die anfängliche Größe des L2-Cache beträgt 256 KB; am 18. August 1997 erreichte es 1024 KB. Die maximale Größe beträgt 2048 KB. Der Cache der ersten Ebene bleibt gleich: 8 KB + 8 KB. Es hatte Taktfrequenzen von 150, 166, 180, 200 MHz.

Pentium PRO-Prozessoren wurden in SPGA-Gehäusen (Staggered Pin Grid Array) mit Pin-Array hergestellt. In einem Gehäuse wurden zwei Kristalle verbaut – ein Prozessorkern und ein selbstgebauter Second-Level-Cache. Installiert in Sockel 8 mit der Möglichkeit, bis zu 4 Prozessoren für symmetrisches Multiprocessing zu kombinieren. Bus 60-66 MHz. Beim 32-Bit-Computing und Multitasking übertraf er den Pentium deutlich, war ihm bei 16-Bit-Anwendungen jedoch unterlegen. Der 150-MHz-Prozessor wurde mit einer 0,60-Mikrometer-Prozesstechnologie hergestellt, ältere Modelle mit 0,35 Mikrometern. Der Pentium PRO bestand aus mehr als 5,5 Millionen Transistoren, plus 15,5 bis 31 Millionen inklusive Cache. Pentium MMX

Der Prozessor wurde am 8. Januar 1997 veröffentlicht Pentium mit MMX-Technologie(Code Name P55), eine Fortsetzung der Pentium-Reihe, in der erstmals ein neuer Satz von 57 MMX-Befehlen (Multi Media eXtention) implementiert wurde, wodurch die Computerleistung in Multimedia-Anwendungen erheblich gesteigert wurde (von 10 bis 60 %, je nach Optimierung).

Es wurde mit Taktfrequenzen von 166, 200 und 233 MHz produziert. Arbeitete an einem 66-MHz-Bus. Im Vergleich zum Pentium wurde die Größe des First-Level-Caches verdoppelt, die sich auf 32 KB belief. Wie in den Vorgängerversionen wurde ein separater Cache verwendet: 16 KB für Daten und 16 KB für Anweisungen. Es ist erwähnenswert, dass diese Aufteilung (und Größe) des L1-Caches seit vielen Jahren zu einer Art Standard geworden ist. Der Second-Level-Cache blieb wie beim Vorgänger auf der Hauptplatine und konnte ein Volumen von bis zu 1 MB haben. Die Prozessoren wurden in 0,35-Mikron-Technologie hergestellt und bestanden aus 4,5 Millionen Transistoren. Entwickelt für Sockel 7.

Pentium II

Die ersten Prozessoren namens Pentium II erschienen am 7. Mai 1997. Diese Prozessoren kombinieren Pentium PRO-Architektur und MMX-Technologie. Im Vergleich zum Pentium Pro ist die Größe des Primärcaches verdoppelt (16 KB + 16 KB). Der Prozessor nutzt eine neue Gehäusetechnologie – eine Kartusche mit aufgedrucktem Randstecker, der den Systembus trägt: S.E.C.C (Single Edge Contact Cartridge). Es wurde im Slot-1-Design produziert, was natürlich ein Upgrade alter Mainboards erforderte. Eine Kassette mit den Maßen 14 x 6,2 x 1,6 cm enthält einen Prozessorkernchip (CPU Core), mehrere Chips, die den sekundären Cache implementieren, sowie diskrete Hilfselemente (Widerstände und Kondensatoren).

Dieser Ansatz kann als Rückschritt betrachtet werden – Intel hatte bereits die Technologie entwickelt, einen Second-Level-Cache in den Kern zu integrieren. Aber auf diese Weise war es möglich, Speicherchips von Drittherstellern zu verwenden. Intel hielt diesen Ansatz einst für vielversprechend für die nächsten 10 Jahre, gab ihn jedoch nach kurzer Zeit wieder auf.

Gleichzeitig bleibt die Unabhängigkeit des sekundären Cache-Speicherbusses erhalten, der über einen eigenen lokalen Bus eng mit dem Prozessorkern verbunden ist. Die Frequenz dieses Busses betrug die Hälfte der Kernfrequenz. Der Pentium II verfügte also über einen großen Cache, der mit halber Prozessorgeschwindigkeit lief.

Die ersten Pentium-II-Prozessoren (Codename Klamath), das am 7. Mai 1997 erschien, bestand allein im Prozessorkern aus etwa 7,5 Millionen Transistoren und wurde in 0,35-Mikron-Technologie implementiert. Sie hatten Kerntaktraten von 233, 266 und 300 MHz bei einer Systembusfrequenz von 66 MHz. Gleichzeitig lief der sekundäre Cache mit halber Kernfrequenz und hatte ein Volumen von 512 KB. Für diese Prozessoren wurde Slot 1 entwickelt, dessen Signalzusammensetzung dem Sockel 8 für den Pentium Pro sehr ähnlich ist. In Steckplatz 1 können jedoch nur zwei Prozessoren kombiniert werden, um ein symmetrisches Multiprozessorsystem oder ein System mit redundanter Funktionssteuerung (FRC) zu implementieren. Dieser Prozessor ist also ein schnellerer Pentium Pro mit MMX-Unterstützung, jedoch mit eingeschränkter Multiprocessing-Unterstützung.

Am 26. Januar 1998 wurde ein Prozessor der Pentium II-Reihe mit dem Kernnamen veröffentlicht – Deschutet. Aus Klamath zeichneten sich durch einen dünneren technologischen Prozess aus – 0,25 Mikrometer und eine Busfrequenz von 100 MHz. Es hatte Taktfrequenzen von 350, 400, 450 MHz. Es wurde im S.E.C.C-Design hergestellt, das bei älteren Modellen durch S.E.C.C.2 ersetzt wurde – ein Cache auf einer Seite des Kerns und nicht auf beiden, wie bei den Standard-Deschutes, und eine modifizierte Kühlerhalterung. Der letzte offiziell in Pentium II-Prozessoren verwendete Kern, obwohl die neuesten Pentium II 350-450-Modelle mit einem Kern ausgestattet waren, der eher an Katmai erinnerte – natürlich nur mit einem abgespeckten SSE. Die MMX-Unterstützung bleibt bestehen. Der Cache der ersten Ebene ist genauso groß wie 32 KB (16 + 16). Auch der Second-Level-Cache hat sich nicht verändert – 512 KB laufen mit halber Taktung. Der Prozessor bestand aus 7,5 Millionen Transistoren und wurde für den Slot-1-Anschluss produziert.

Pentium II OverDrive- Dies war der Name des Prozessors, der am 11. August 1998 veröffentlicht wurde, um den Pentium PRO auf älteren Prozessoren aufzurüsten Motherboards oh, und arbeiten in Sockel 8).

Hatte einen Codenamen P6T. Hatte eine Frequenz von 333 MHz. Der First-Level-Cache war 16 KB für Daten + 16 KB für Anweisungen groß, der Second-Level-Cache hatte eine Größe von 512 KB und war in den Kernel integriert. Arbeitete mit Prozessorfrequenz. Bus 66 MHz. Enthält 7,5 Millionen Transistoren und wurde mit der 0,25-Mikron-Prozesstechnologie hergestellt. Unterstützt den MMX-Befehlssatz.

Ein neuer Zweig in Richtung Mikroprozessortechnologie für Intel war die Veröffentlichung paralleler Haupt-, „leichter“ und billigerer Optionen. Das ist die Serie Celeron. Am 15. April 1998 rief der erste Prozessor an Celeron und arbeitet mit einer Taktfrequenz von 266 MHz.

Code Name Covington. Bei diesem Prozessor handelt es sich um einen „abgespeckten“ Pentium II. Celeron basiert auf dem Kern Deschutet ohne Second-Level-Cache. Was sich natürlich auf seine Leistung auswirkte. Aber es beschleunigte einfach hervorragend (von eineinhalb auf zwei). Wenn Pentium-Übertaktung II durch die maximale Cache-Frequenz begrenzt war, dann war sie einfach nicht da!

Celeron arbeitete auf einem 66-MHz-Bus und wiederholte alle Hauptmerkmale seines Vorfahren – Pentium II Deschutes: Cache der ersten Ebene – 16 KB + 16 KB, MMX, 0,25 Mikron-Prozesstechnologie. 7,5 Millionen Transistoren. Der Prozessor wurde ohne Schutzkassette hergestellt – ein Design – S.E.P.P (Single Edge Pin Package). Anschluss – Steckplatz 1.

Ab 300 MHz erschienen Celeron-Prozessoren mit einem im Kern integrierten 128 KB großen L2-Cache, der mit der Prozessorfrequenz arbeitete. Code Name - Mendocino. Veröffentlicht am 8. August 1998. Dank des Full-Speed-Cache verfügt es über eine mit dem Pentium II vergleichbare hohe Leistung (bei gleicher Systembusfrequenz). Sie wurden mit Taktfrequenzen von 300 bis 533 MHz produziert. Am 30. November 1998 wurde eine Prozessorversion im P.P.G.A-Design (Plastic Pin Grid Array) veröffentlicht, die im Sockel 370-Anschluss funktionierte.

Bis 433 MHz wurde es in zwei Ausführungen hergestellt: S.E.P.P und P.P.G.A. Eine Zeit lang gab es parallel die Optionen Slot-1 (266 – 433 MHz) und Socket-370 (300A – 533 MHz), am Ende wurde die erste nach und nach durch die letztere ersetzt.

Der neue Celeron war ein Schritt in Richtung Pentium!!!, da er aber auf einem 66-MHz-Bus lief, konnte er nicht alle Vorteile des integrierten High-Speed-Cache ausspielen. Da der Cache in den Kern integriert wurde, erhöhte sich die Anzahl der Transistoren, aus denen der Prozessor besteht, erheblich – 19 Millionen. Der technische Prozess blieb gleich – 0,25 Mikrometer.

Für leistungsstarke Computer beabsichtigte Familie Xeon. Pentium II Xeon ist eine Serverversion des Pentium II-Prozessors, der den Pentium PRO ersetzte. Mit Kern produziert Deschutet und unterschied sich vom Pentium II durch seinen schnelleren (Full-Speed) und größeren (es gibt Optionen mit 1 oder 2 MB) Second-Level-Cache und Design. Er wurde im S.E.C.C-Design für Steckplatz 2 hergestellt. Dies ist ebenfalls ein Randstecker, jedoch mit 330 Kontakten, einem VRM-Spannungsregler und einem EEPROM-Speichergerät. Kann in Multiprozessorkonfigurationen arbeiten. Es wurde am 29. Juni 1998 veröffentlicht.

Der Second-Level-Cache arbeitet wie beim Pentium PRO mit voller Geschwindigkeit. Nur befindet es sich hier auf derselben Platine wie der Prozessor und ist nicht in den Kern integriert. Cache der ersten Ebene – 16 KB + 16 KB. Busfrequenz – 100 MHz. Unterstützt den MMX-Befehlssatz. Der Prozessor arbeitete mit Frequenzen von 400 und 450 MHz. Hergestellt mit der 0,25-Mikron-Prozesstechnologie. und enthielt 7,5 Millionen Transistoren.

Hier endet die Entwicklung der Pentium II-Reihe. Beginnend mit dem Pentium II hat Intel drei Hauptrichtungen bei der Produktion von Prozessoren unterschieden: Pentium– Hochleistungsprozessor für Workstations und den Heimgebrauch, Celeron– eine Budgetversion des Pentium für das Büro oder zu Hause, Xeon– Serverversion mit erhöhter Leistung.

Pentium!!!

Die ersten Prozessoren mit dem Namen Pentium!!! nicht viel anders als der Pentium II. Sie arbeiteten auf demselben Bus mit einer Frequenz von 100 MHz (später, ab dem 27. September 1999, erschienen Modelle, die auf einem 133-MHz-Bus arbeiteten) und wurden im S.E.C.C.-Design hergestellt. 2 und wurden für den Einbau in Steckplatz 1 konzipiert.

Der Cache-Speicher bleibt gleich: L1 – 16 KB + 16 KB. L2 – 512 KB, befindet sich auf der Prozessorplatine und arbeitet mit der halben Prozessorfrequenz. Der Hauptunterschied besteht in der Erweiterung des SIMD-Befehlssatzes – SSE (Streaming SIMD Extensions). Auch der Satz an MMX-Befehlen wurde erweitert und der Mechanismus für den Streaming-Speicherzugriff verbessert. Kernel-Codename Katmai. Veröffentlicht am 26. Februar 1999. Der Prozessor arbeitete mit Frequenzen von 450–600 MHz und enthielt 9,5 Millionen Transistoren. Genau wie sein Vorgänger wurde der Pentium II Deschutes mit der 0,25-Mikron-Prozesstechnologie hergestellt.

Kupfermine– so hieß der nächste Pentium!!!-Prozessorkern, der Katmai am 25. Oktober 1999 ablöste. Tatsächlich handelt es sich bei Coppermine um einen neuen Prozessor und nicht um eine Überarbeitung von Deschutes. Der neue Prozessor verfügt über einen in den Kern integrierten Full-Speed-Second-Level-Cache von 256 KB (Advanced Transfer Cache).

Hergestellt mit der 0,18-Mikron-Prozesstechnologie. Die Verdünnung der Technologie von 0,25 auf 0,18 Mikrometer ermöglichte die Platzierung auf dem Kern größere Zahl Transistoren und jetzt gibt es 28 Millionen davon, gegenüber 9,5 Millionen im alten Katmai. Zwar betrifft der Großteil der neu eingeführten Transistoren den integrierten L2-Cache. Der L1-Cache blieb unverändert. Unterstützte MMX- und SSE-Befehlssätze. Zuerst im S.E.C.C.-Design hergestellt. 2, aber da der Cache nun in den Prozessorkern integriert war, war die Prozessorplatine überflüssig und erhöhte nur die Kosten des Prozessors. Daher kamen bald Prozessoren im FC-PGA-Design (Flip-Chip PGA) auf den Markt. Wie der Celeron Mendocino arbeiteten sie im Sockel 370-Anschluss.

Zwar gab es eine eingeschränkte Kompatibilität mit älteren Motherboards. Da der Prozessor nun mit höheren Taktraten lief, befand sich der Kern oben und hatte direkten Kontakt zum Kühlkörper. Coppermine war der letzte Prozessor für Steckplatz 1. Er arbeitete auf einem 100- und 133-MHz-Bus (im Namen des Prozessors wurde der 133. Bus mit dem Buchstaben bezeichnet). B, zum Beispiel – Pentium !!! 750B). Prozessoren mit dem Coppermine-Kern arbeiteten mit Taktraten von 533 bis 1200 MHz. Die ersten Versuche, einen Prozessor auf diesem Kern mit einer Frequenz von 1113 MHz freizugeben, scheiterten, da er in extremen Modi sehr instabil war, und alle Prozessoren mit dieser Frequenz wurden zurückgerufen – dieser Vorfall hat den Ruf von Intel stark geschädigt.

Kern Tualatin ersetzte Coppermine am 21. Juni 2001. Zu diesem Zeitpunkt waren bereits die ersten Pentium-4-Prozessoren auf dem Markt, und der neue Prozessor sollte die neuen 0,13 Mikrometer testen. Technologie, und auch um die Nische der Hochleistungsprozessoren zu füllen, da die Leistung des ersten Pentium 4 recht gering war. Tualatin ist der ursprüngliche Name von Intels globalem Projekt zur Umstellung der Prozessorproduktion auf 0,13-Mikron-Technologie. Die Prozessoren selbst mit dem neuen Kern waren die ersten Produkte, die im Rahmen dieses Projekts erschienen.

Im Kernel selbst gibt es nur wenige Änderungen – lediglich die „Data Prefetch Logic“-Technologie wurde hinzugefügt. Es verbessert die Leistung, indem es die von der Anwendung benötigten Daten vorab in den Cache lädt. Darüber hinaus liegt der Unterschied zwischen diesen Kernen in der verwendeten Produktionstechnologie – Coppermine wird mit der 0,18-Mikron-Technologie und Tualatin mit der 0,13-Mikron-Technologie hergestellt. Der Sockel für den neuen Prozessor bleibt derselbe – Sockel 370, aber das Design wurde auf FC-PGA 2 geändert, der in Pentium 4-Prozessoren verwendet wurde. Er unterscheidet sich vom alten FC-PGA vor allem dadurch, dass der Kern mit einer Wärme bedeckt ist -ableitende Platte, die ihn auch vor Beschädigungen beim Einbau des Kühlers schützt.

Viel Spaß mit Tualatin, Pentium Line!!! in zwei Klassen „aufgeteilt“ – Desktop- und Serverprozessoren. Bei Ersterem blieb das L2-Cache-Volumen gleich 256 KB, bei Letzterem verdoppelte es sich auf 512 KB; Außerdem fehlte der Desktop-Version des neuen P-III (dem sogenannten Desktop Tualatin) die SMP-Unterstützung. Cache der ersten Ebene – 16 KB + 16 KB. Es muss gesagt werden, dass Desktop Tualatin nicht lange hielt: Es wurde nur an große PC-Monteure geliefert und vom Markt genommen, um nicht mit dem Pentium 4 zu konkurrieren. Aber der Pentium !!!-S, die Serverversion von Der Prozessor sollte die Nische der leistungsstarken Serverprozessoren besetzen, da die Leistung von Xeon-Prozessoren nicht mehr ausreichte und der Pentium 4 keine SMP-Unterstützung hatte und insgesamt eine eher geringe Leistung zeigte.

Wie oben erwähnt, wurden Tualatin-Prozessoren mit einem fortschrittlicheren 0,13-Mikron-Prozessor hergestellt. technischer Prozess, der auf einem Bus mit einer Frequenz von 133 MHz betrieben wurde und aus 44 Millionen Transistoren bestand. Unterstützte MMX- und SSE-Befehlssätze. Der Prozessor arbeitete mit Frequenzen von 1 GHz bis 1,33 GHz (Desktop Tualatin) und von 1,13 GHz bis 1,4 GHz (Serverversion).

Erst kürzlich habe ich einige ziemlich interessante Informationen erfahren – es stellte sich heraus, dass Intel einen Prozessor entwickelte, der eine Fortsetzung der Pentium-Reihe sein sollte!!! Dieser Prozessor basierte auf einem verbesserten Tualatin-Kern mit 0,13 Mikrometern. technischer Prozess. Der Hauptunterschied zum üblichen Tualatin bestand in der Vergrößerung auf 1024 KB. L2-Cache und 166-MHz-Systembus! Die Frequenzen mussten mindestens 2,0 GHz erreichen. Doch Intel, das auf den Pentium-4-Prozessor setzt, lehnt den neuen Tualatin ab. Denn selbst wenn der Celeron Tualatin, übertaktet auf Frequenzen von etwa 1,7 GHz, nicht nur problemlos mit dem Celeron Willamette, sondern auch mit dem Pentium 4 konkurriert, kann der neue Tualatin, der mit einem riesigen Cache und einem schnellen Bus ausgestattet ist, dies nicht tun Lass ihnen keine Chance.

Nach der Veröffentlichung der Pentium!!!-Prozessoren veröffentlichte Intel weiterhin die Celeron-Reihe, um seine Position auf dem Markt für Budgetprozessoren nicht zu verlieren. Nun handelte es sich um völlig unterschiedliche Prozessoren – Intel wiederholt die Erfahrung bei der Entwicklung der ersten Prozessoren namens Celeron: Er verwendet den Pentium-Prozessorkern!!! mit einem auf 128 KB reduzierten Second-Level-Cache und einem langsamen 66-MHz-Bus.

29. März 2000 Die ersten Celeron-Core-Prozessoren erscheinen Kupfermine 128 oder Coppermine Lite.

Wie der Name schon sagt, basiert der Prozessor auf dem Coppermine-Kern mit halbiertem Second-Level-Cache. Genau wie sein älterer Bruder - Pentium!!! Coppermine, der neue Celeron, verfügt über eine Reihe zusätzlicher SSE-Befehle, einen schnellen integrierten Cache-Speicher und wird nach dem gleichen technologischen Standard (0,18 Mikrometer) hergestellt und unterscheidet sich nur in der Größe des Second-Level-Cache – 128 KB gegenüber 256 KB für den Pentium!!! (Das Anstößigste ist, dass der Cache physisch im Prozessor vorhanden ist und einfach deaktiviert ist.) Funktioniert im gleichen Socket 370-Anschluss.

Die ersten Prozessoren erschienen mit einer Frequenz von 566 MHz und liefen auf einem 66-MHz-Bus. Später, am 3. Januar 2001, mit der Veröffentlichung der 800-MHz-Version, wechselte Celeron zu einem schnelleren 100-MHz-Bus. Die maximale Frequenz dieser Prozessoren betrug 1100 MHz. Cache der Ebene 1: 32 KB (16 KB für Daten und 16 KB für Anweisungen). Der Prozessor bestand aus 28,1 Millionen Transistoren.

Noch nie war ein Celeron so nah an einem Pentium-Prozessor. Von Pentium!!! Desktop-Tualatin unterschied sich nur durch einen langsameren 100-MHz-Bus. Im Allgemeinen hat Intel den „neuen Celeron“ herausgebracht, indem er die Größe des Second-Level-Cache unverändert ließ und die FSB-Frequenz für den Tualatin-Kern für den Desktop-Einsatz auf 100 MHz reduzierte. Die Prozessoren wurden mit Taktfrequenzen von 900 MHz bis 1400 MHz hergestellt, bestanden aus 44 Millionen Transistoren und unterstützten MMX, SSE. Technologischer Prozess 0,13 Mikrometer. Sie wurden im FC-PGA 2-Design für den Socket 370-Anschluss hergestellt.

Frohe Pentium-Veröffentlichung!!! Intel produziert weiterhin Serverprozessoren basierend auf dem Pentium der neuen Generation. Am 17. März 1999 wurde der erste Prozessor der Pentium-Reihe veröffentlicht!!! Xeon.

Kernel-Codename Gerber. Wurde auf Pentium-Basis gebaut!!! Katmai. Enthält 512, 1024 oder 2048 KB Full-Speed-Speichercache der zweiten Ebene. Cache der ersten Ebene – 16 KB + 16 KB. Hergestellt mit Frequenzen von 500 und 550 MHz unter Verwendung von 0,25 Mikrometern. technischer Prozess und bestand aus 9,5 Millionen Transistoren. Wird auf einem 100-MHz-Systembus betrieben. Es wurde im S.E.C.C-Design für Steckplatz 2 hergestellt. Es war für den Einsatz in Servern und Workstations mit zwei, vier, acht Prozessoren (oder mehr) vorgesehen.

Glücklicher Übergang zu Pentium!!! Auf dem neuen Kern erschien am 25. Oktober 1999 eine Modifikation des Xeon-Prozessors mit einem neuen Kern Kaskaden. Es handelte sich im Wesentlichen um einen verbesserten Coppermine-Kern. Der Prozessor verfügte über 256 KB bis 2048 KB Second-Level-Speichercache und wurde mit Systembusfrequenzen von 100 und 133 MHz (je nach Version) betrieben. Prozessoren wurden mit Frequenzen von 600 bis 900 MHz hergestellt. Prozessoren mit einer Frequenz von 900 MHz aus den ersten Chargen überhitzten und ihre Lieferungen wurden vorübergehend eingestellt. Xeon Cascades wurde wie sein Vorgänger für den Einbau in den Slot-2-Anschluss konzipiert und mit 0,18 Mikrometer gefertigt. technischer Prozess und bestand aus 28,1 Millionen Transistoren. Könnte in Servern und Workstations mit zwei, vier und acht Prozessoren funktionieren.

Kernelbasiert Tualatin Xeon-Prozessoren wurden nicht veröffentlicht. An ihre Stelle trat der oben beschriebene Pentium!!!-S. Xeon-Prozessoren Unterstützte MMX- und SSE-Befehlssätze.

Pentium 4

Beim Versuch, die Frequenz eines Pentium-Prozessors zu erhöhen, stoßen wir auf viele Probleme!!! Beim Coppermine-Kern über 1 GHz erkannten die Intel-Ingenieure, dass die alte Prozessorarchitektur, die seit dem Pentium Pro unverändert blieb, radikale Änderungen erforderte. Und obwohl der Übergang zur 0,13-Mikron-Produktion Pentium helfen wird!!! Es wird etwa ein Jahr dauern, bis es seine Arbeit ganz gut erledigt, das Potenzial dieser Architektur ist fast ausgeschöpft und das Unternehmen hat eine neue Architektur für seine neuen 32-Bit-Prozessoren entwickelt, die es Intel NetBurst Micro-Architecture nennt. Damit Prozessoren mit Frequenzen von mehreren Gigahertz arbeiten können, erhöht Intel die Länge der Pentium 4-Pipeline auf 20 Stufen (Hyper Pipelined Technology), wodurch auch mit technologischen Standards ein Prozessorbetrieb mit einer Frequenz von 2 GHz erreicht werden konnte von 0,18 Mikrometern. Aufgrund dieser Vergrößerung der Pipelinelänge nimmt jedoch auch die Ausführungszeit eines Befehls in Prozessorzyklen stark zu. Daher hat das Unternehmen intensiv an Algorithmen zur Übergangsvorhersage (Advanced Dynamic Execution) gearbeitet.

Der Level-1-Cache im Prozessor hat erhebliche Änderungen erfahren. Im Gegensatz zum Pentium!!!, dessen Cache Anweisungen und Daten speichern konnte, verfügt der Pentium 4 nur über einen 8 KB großen Datencache. Befehle werden im sogenannten Trace Cache gespeichert. Dort werden sie bereits in dekodierter Form gespeichert, d. h. in Form einer Folge von Mikrooperationen, die zur Ausführung in den Aktoren des Prozessors empfangen werden. Die Kapazität dieses Caches beträgt 12.000 Mikrooperationen.

Auch im neuen Prozessor wurde der Befehlssatz erweitert - SSE2. Zu den 70 SSE-Anweisungen kamen weitere 144 neue Anweisungen hinzu. Eine der vielen Neuerungen war ein völlig neuer 100-MHz-Bus, der 4 Datenpakete pro Takt überträgt – QPB (Q uad P behindert B uns), was eine resultierende Frequenz von 400 MHz ergibt.

Der erste der Pentium 4-Reihe war ein Prozessor mit Kern Willamette 423.

Diese am 20. November 2000 mit Frequenzen von 1,4 und 1,5 GHz auf den Markt gebrachten Prozessoren, die mit der 0,18-Mikron-Prozesstechnologie hergestellt wurden, erreichten eine Frequenz von 2 GHz. Der Prozessor wurde im neuen Sockel 423 verbaut und im FC-PGA 2-Design gefertigt. Er bestand aus 42 Millionen Transistoren.

Der Cache der 2. Ebene blieb gleich groß – 256 KB. Die Breite des L2-Cache-Busses beträgt 256 Bit, die Cache-Latenz wurde jedoch halbiert, sodass 48 GB Cache-Bandbreite bei 1,5 GHz möglich sind.

Da die Architektur des neuen Prozessors in erster Linie auf die Erhöhung der Taktfrequenz ausgerichtet war, ist es nicht verwunderlich, dass die ersten Pentium 4-Prozessoren eine extrem geringe Leistung aufweisen. Bei den meisten Aufgaben war der 1,4 GHz Prozessor dem Pentium unterlegen!!! Coppermine, Betrieb mit 1000 MHz.

Später, am 27. August 2001, Prozessoren mit dem Kern Willamette vorgesehen für den Einbau in den neuen Anschluss - Sockel 478. Der Prozessor wiederholte alle Eigenschaften seines Vorfahren, mit Ausnahme des Designs - mPGA und des Sockel 478-Anschlusses.

Der bisherige Sockel-423-Formfaktor war „vorübergehend“ und Intel wird ihn in Zukunft nicht mehr unterstützen. Die Größe des Prozessors wurde reduziert, da die Pins nun direkt unter dem Prozessorkern angebracht sind. Dieser Prozessor arbeitete wie sein Vorgänger mit Frequenzen von 1,4 bis 2,0 GHz.

Northwood– so heißt der nächste Kern, auf dem bis heute Pentium 4-Prozessoren produziert werden.

Gehen Sie zu 0,13 µm. Durch den technischen Prozess war es möglich, die Taktfrequenz weiter zu erhöhen und den Second-Level-Cache auf 512 KB zu vergrößern. Auch die Anzahl der Transistoren, aus denen der Prozessor besteht, ist gestiegen – mittlerweile sind es 55 Millionen. Selbstverständlich bleibt die Unterstützung für die Befehlssätze MMX, SSE und SSE2 bestehen.

Die ersten Prozessoren auf Basis des Northwood-Kerns erschienen am 7. August 2001 mit einer Frequenz von 2,0 GHz und einer Systembusfrequenz von 400 MHz (4 * 100 MHz). Heute arbeiten Northwood-Prozessoren mit Frequenzen von 1,6 bis 3,2 GHz. Um Verwechslungen mit Prozessoren zu vermeiden, die mit den gleichen Frequenzen, aber unterschiedlichen Kernen arbeiten, verwendet Intel erneut Buchstabenmarkierungen. Zum Beispiel Pentium 1.8 A, wo der Buchstabe A weist auf einen neuen Kern und einen größeren L2-Cache hin.

Am 6. Mai 2002 veröffentlichte Intel einen Prozessor auf Basis des Northwood-Kerns mit einer Systembusfrequenz von 533 MHz (4 * 133 MHz) und einer Taktfrequenz von 2,26 GHz. Da Modelle mit einer Busfrequenz von 400 MHz mit Frequenzen bis 2,6 GHz produziert wurden, wurden auch hier Buchstabenmarkierungen verwendet. Genau wie bei Pentium-Prozessoren!!! Das Vorhandensein eines 133-MHz-Busses wurde durch den Buchstaben angezeigt B. Zum Beispiel Pentium 4 2.4 B.

Aber Intel hört hier nicht auf und veröffentlichte am 14. April 2003 einen Prozessor auf Basis des gleichen Northwood-Kerns, jedoch mit einer Systembusfrequenz von 800 MHz (4 * 200 MHz) und einer Taktfrequenz von 3,0 GHz. Später wurden Prozessoren mit einem 800-MHz-Systembus mit niedrigeren Frequenzen produziert – ab 2,4 GHz. Um einen neuen Bus anzuzeigen, erscheint ein Buchstabe in der Prozessormarkierung C. Zum Beispiel Pentium 4 2.4 C. (Es gibt also drei Modifikationen des 2,4-GHz-Prozessors mit unterschiedlichen Busfrequenzen, die sich um den Faktor 2 unterscheiden!)

Alle 800-MHz-FSB-Prozessoren unterstützen die neue Technologie HT, welches dafür steht Hyper-Threading.

Pentium 4HT

Am 14. November 2002 wurde der Pentium 4-Prozessor mit einer Frequenz von 3,06 GHz und einer Systembusfrequenz von 533 MHz mit Unterstützung veröffentlicht neue Technologie Hyper-Threading.

Ein physischer Prozessor mit Hyper-Threading wird vom System als zwei betrachtet, wodurch Sie die Auslastung seiner Ressourcen optimieren und die Leistung verbessern können. Das Funktionsprinzip von Hyper-Threading basiert darauf, dass bei der Ausführung zu jedem Zeitpunkt nur ein Teil der Prozessorressourcen beansprucht wird Programmcode. Auch ungenutzte Ressourcen können mit Arbeit belastet werden – so kann beispielsweise eine andere Anwendung (oder ein anderer Thread derselben Anwendung) zur parallelen Ausführung genutzt werden.

HT ist kein echtes Multiprocessing, da sich die Anzahl der Blöcke, die Befehle direkt ausführen, nicht geändert hat. Lediglich die Effizienz ihres Einsatzes ist gestiegen. Daher ist der Leistungsgewinn umso höher, je besser ein bestimmtes Programm für HT optimiert ist. Laut Intel kann der Vorteil von HT 30 % erreichen, während die Blöcke, die ihn implementieren, weniger als 5 % der Gesamtfläche des Pentium 4-Chips einnehmen. Allerdings können beispielsweise auch perfekt optimierte Anwendungen auf Daten zugreifen, die befindet sich nicht im Cache-Prozessorspeicher, sodass dieser im Leerlauf ist. Wenn die NetBurst-Architektur selbst darauf ausgelegt war, die Anzahl der Megahertz zu erhöhen, ist Hyper-Threading im Gegenteil darauf ausgelegt, die pro Taktzyklus geleistete Arbeit zu erhöhen.

Einer der Gründe für die relativ späte Einführung von Hyper-Threading im Pentium 4 (Unterstützung gibt es nicht nur im Northwood-Kern, sondern sogar in Willamette, wurde aber blockiert) war die relativ geringe Verbreitung von Windows XP – dem einzigen Betriebssystem im Pentium 4 Windows-Familie, die die neue Technologie vollständig unterstützt. Die Technologie muss auch vom Chipsatz und BIOS des Motherboards unterstützt werden.

Heute wird die Hyper-Threading-Technologie vom Pentium 4 3,06 GHz-Prozessor mit einer Systembusfrequenz von 533 MHz sowie von allen Prozessoren mit einer Busfrequenz von 800 MHz unterstützt.

Nach der Veröffentlichung des Pentium 4 Willamette für Sockel 478 bringt Intel Celeron auf Basis des Pentium 4 Willamette für Sockel 478 heraus, um Prozessoren für Sockel 370 vom Markt zu verdrängen und auch die Nische der Budget-Prozessoren zu besetzen (wo zuvor Celeron Tualatin gewesen war). Kern Willamette 128.

Der Willamette 128-Kern unterscheidet sich architektonisch nicht vom Pentium 4 Willamette-Kern. Die Organisation des Caches und seine Betriebsalgorithmen haben sich nicht geändert, der einzige Unterschied ist die Größe – 128 KB Second-Level-Cache statt 256 KB beim ursprünglichen Pentium 4 Willamette.

Selbstverständlich bleibt auch der Sockel-478-Formfaktor erhalten, den Intel schon länger nutzen will. Damit überführt Intel seine Prozessoren auf eine Plattform, sodass Sie bei einem späteren Upgrade nicht das Motherboard samt Prozessor wechseln müssen.

Am 15. Mai 2002 erschien der erste Prozessor namens Celeron, basierend auf dem Pentium 4, mit einer Frequenz von 1,7 GHz. Später, am 12. Juni 2002, erscheint eine 1,8-GHz-Version.

Der neue Celeron nutzt wie bisher einen 100-MHz-Systembus, allerdings nun mit der Übertragung von 4 Signalen pro Takt. Der vierfache 100-MHz-FSB löst endlich das alte Celeron-Problem der fehlenden FSB-Bandbreite.

Wie der Pentium 4 Willamette besteht auch der neue Celeron aus 0,18 Mikrometern. technischer Prozess. Besteht aus 42 Millionen Transistoren. Erhältlich mit den Frequenzen 1,7 und 1,8 GHz.

Der nächste und letzte Kern des Celeron-Prozessors ist heute Northwood(natürlich mit auf 128 KB gekürztem Second-Level-Cache). Der erste Prozessor, der auf diesem Kern basierte, war der Celeron 2,0 GHz, der am 18. September 2002 auf den Markt kam. Er wiederholt wie der Celeron Willamette 128 vollständig die Eigenschaften seines älteren Bruders Pentium 4 Northwood, mit Ausnahme eines ausschließlich für 400 MHz (4 * 100 MHz) ausgelegten Busses und eines 128 KB großen Second-Level-Cache.

Anwendung 0,13 Mikrometer. Der technische Prozess bietet den Vorteil einer guten Übertaktbarkeit. Der Northwood-Kern verfügt über ein gutes Frequenzpotenzial (aktuell bis zu 3,2 GHz), sodass Spielraum für Übertaktung besteht.

Seit der ersten Veröffentlichung des Intel Pentium II Xeon sind etwas weniger als drei Jahre vergangen. Und Intel setzt am 21. Mai 2001 seinen Kurs der Segmentierung seiner Prozessoren fort und kündigt den Xeon-Prozessor der nächsten Generation an, der darauf basiert Pentium-Kern 4 Willamette. Der Prozessor heißt altmodisch Intel Xeon und ist in drei Varianten erhältlich: 1,4 GHz, 1,5 GHz und 1,7 GHz. Der Prozessorkern ist bis auf kleinere Details nahezu identisch mit der regulären (Desktop-)Version des Pentium 4. Damit verfügt der neue Xeon über alles, was der Pentium 4 hat – sowohl die Vorteile der neuen Architektur als auch deren Nachteile.

Die ersten Xeon-Modelle wurden mit 0,18 Mikron hergestellt. technischer Prozess, dessen Kern fast identisch mit dem Pentium 4 Willamette war und den Codenamen trug Fördern. Der Prozessor wurde mit Taktraten bis 2,0 GHz produziert. Bestehend aus 42 Millionen Transistoren.

Cache-Speicher der Stufe 1, wie alle Prozessoren der Pentium 4-Reihe, mit NetBurst-Architektur, 8 KB Datencache. Cache der zweiten Ebene – 256 KB mit verbesserter Datenübertragung (256 KB Advanced Transfer Cache). Genau wie der Pentium 4 Willamette nutzt der neue Xeon einen 400-MHz-Systembus (4 * 100 MHz), der zwei Speicherkanäle synchron mit einer Frequenz von 400 MHz betreibt.

Historisch gesehen wurde bei den Intel Xeon-Prozessorlinien (d. h. Pentium II Xeon, Pentium III Xeon) immer ein anderer Prozessor verwendet reguläre Versionen Prozessordesign Während die Pentium II- und Pentium III-Prozessoren in einer 242-Pin-Slot-1-Version hergestellt wurden, verwendeten ihre Xeon-Versionen einen 330-Pin-Slot-2-Anschluss. Die meisten zusätzlichen Beine wurden verwendet, um den Chip mit zusätzlicher Energie zu versorgen. Mit zwei Megabyte L2-Cache verbrauchte der Pentium III Xeon mehr Strom als sein 256-KB-Pendant. Eine ähnliche Situation trat beim neuen Xeon auf. Während die ersten Pentium 4 Willamette-Prozessoren einen 423-Pin-Sockel verwendeten, verwendet der Xeon eine 603-Pin-Schnittstelle, die für den Einsatz im Sockel 603 konzipiert ist. Der Prozessor kann nur in Einzel- oder Doppelprozessorkonfigurationen betrieben werden.

Am 9. Januar 2002 erschienen Xeon-Prozessoren, die auf dem Northwood-Kern mit 0,13 Mikrometern basieren. technisch prozessorientiert und mit einem 512 KB großen Second-Level-Cache ausgestattet. Kernel-Codename – Prestonia. Er unterscheidet sich von seinem Vorgänger, dem Xeon Foster, lediglich durch den größeren Cache und den fortschrittlicheren technischen Prozess. Prozessoren arbeiten mit Frequenzen von 1,8 GHz bis 3,0 GHz. Bestehen aus 55 Millionen Transistoren. Prozessoren mit dem Prestonia-Kern unterstützen jetzt erstmals Hyper-Threading.

12. März 2002, der Xeon MP-Prozessor wird veröffentlicht. Hergestellt mit 0,18 Mikron. und ist mit einem 256 KB großen L2-Cache ausgestattet. Der Hauptunterschied zu Xeon Foster-Prozessoren besteht in der Fähigkeit, in Multiprozessorsystemen zu arbeiten. Sie arbeiten mit Frequenzen von 1,4 bis 1,6 GHz. Diese Prozessoren unterstützen auch die Hyper-Threading-Technologie.

Am 4. November 2002 erschienen Xeon MP-Prozessoren, die mit 0,13 Mikrometern hergestellt wurden. technischer Prozess. Diese Prozessoren, die mit Frequenzen von 1,5 GHz, 1,9 GHz und 2,0 GHz arbeiten, unterscheiden sich von ihren Xeon Prestonia-Kollegen nicht nur durch die Fähigkeit, in Multiprozessorkonfigurationen zu arbeiten, sondern auch durch das Vorhandensein eines integrierten Third-Level-Cache von 1 oder 2 MB in Größe. Dadurch ist die Anzahl der Transistoren, aus denen der Prozessor besteht, auf 108 Millionen gestiegen!

Am 18. November 2002 erschienen Xeon-Prozessoren, die auf einem 533-MHz-Systembus (4 * 133 MHz) laufen. Diese Prozessoren basieren auf dem Prestonia-Kern und verwenden 0,13 Mikrometer. technischen Prozess und bestehen aus 108 Millionen Transistoren. Cache-Speicher der zweiten Ebene – 512 KB. Cache der dritten Ebene 1 MB. Xeon-Prozessoren auf dem 533-MHz-Bus sind mit Taktfrequenzen von 2,0 GHz bis 3,06 GHz erhältlich (veröffentlicht am 10. März 2003). Kürzlich wurde auch ein 3,2-GHz-Prozessor angekündigt.

Ende 2003 wird Intel einen neuen Kern für seine Prozessoren vorstellen – Prescott. Diese Prozessoren werden mit 0,09 Mikron hergestellt. (90 nm) Technologie. Der Prescott-Kern wird aus 125 Millionen Transistoren bestehen und 1 MB Second-Level-Cache enthalten. Außerdem ist es möglich, dass der First-Level-Cache endlich auf 32 KB erhöht wird. Selbstverständlich wird der neue Kern die Hyper-Threading-Technologie unterstützen. Nur wird dies bereits passieren Hyper-Threading 2, weitere Entwicklung„Multiprocessing“ in einem Chip. Was ihre Unterschiede sein werden, ist noch nicht bekannt, aber es gibt Annahmen (von niemandem bestätigt), dass Sie mit dem neuen Produkt nicht zwei, sondern mehrere virtuelle Prozessoren in einem physischen Prozessor sehen können.

Außerdem wird ein neuer Befehlssatz hinzugefügt (oder ein bestehender erweitert), darunter 15 neue Anweisungen zur Konvertierung von Gleitkommazahlen in Ganzzahlen, komplexe Zahlenarithmetik, spezielle Anweisungen für die Videodekodierung, SIMD-Anweisungen für das Gleitkommaformat und eine Thread-Synchronisierung Verfahren.

Die ersten Prozessoren mit diesem Kern werden mit Frequenzen von 3,2 und 3,4 GHz arbeiten. Ihre Gehäuse werden mit denen kompatibel sein, die derzeit in Pentium 4 Northwood-Prozessoren verwendet werden. Zukünftig werden Prescott-Prozessoren auf ein neues LGA 775-Gehäuse mit 775 Pins umgestellt, was auch neue Motherboards mit Sockel-T-Anschluss erfordert.

Auf Basis des neuen Kerns wird auch die Produktion von Celeron-Prozessoren fortgesetzt. Nur ist es jetzt überhaupt nicht mehr derselbe Celeron wie zuvor. Celeron-Chips auf Basis des Prescott-Kerns werden nicht nur aufgrund der erhöhten Kerntaktfrequenz schneller sein als ihre Vorgänger auf Basis von Northwood. Sie unterstützen einen Systembus mit einer Frequenz von 533 MHz und ihre Cache-Größe erhöht sich von 128 auf 256 KB. Die ersten Celerons auf Basis des Prescott-Kerns werden Frequenzen von 2,8 und 3,06 GHz haben. Intel hat noch keine Prozessoren mit 90-nm-Technologie auf den Markt gebracht und entwickelt bereits die nächste Generation der Chip-Produktionstechnologie vollständig – mit 65-nm-Standards. Die Entwicklung ist ebenfalls im Gange und es gibt funktionierende Chips, die nicht nur mit 0,065 Mikrometern hergestellt werden. technologischen Prozess, sondern auch 45 nm, 32 nm und sogar 22 nm.

Prescott wird vom Kern gefolgt Tejas mit einem 1066-MHz-Bus. Darauf aufbauend werden acht verschiedene Prozessoren mit Taktfrequenzen von 6 bis 9,2 GHz vorgestellt. Der erste davon soll Ende 2004 in den Handel kommen. Anschließend stellt das Unternehmen den Kern vor Nehalem, das einen 1200-MHz-Systembus nutzt und eine Betriebsfrequenz von über 10 GHz ermöglicht. Nehalem wird vollständig darauf basieren neue Architektur. Es wird kein aufgerüsteter Pentium 4 wie Prescott und Tejas sein. Es wird das LaGrande-Hardwareschutzsystem verwenden und einigen Berichten zufolge wird es eine fortschrittlichere Multithreading-Technologie verwenden. Die Anzahl der Transistoren im Chip wird etwa 150 bis 250 Millionen betragen. Pentium Nehalem soll 2005 erscheinen.

Außerdem wurde kürzlich ein neuer Prozessor aus der Pentium 4-Reihe angekündigt - Intel Pentium 4 Extreme Edition.

Es ist mit der Hyper-Threading-Technologie ausgestattet, läuft auf einem 800-MHz-Systembus und hat eine Kerntaktfrequenz von 3,2 GHz. Der Hauptunterschied zum vorherigen Pentium 4 war jedoch das Vorhandensein eines 2 MB großen L3-Cache-Speichers, der in den Chip integriert war! Dieser Cache-Speicher ergänzt den standardmäßigen 512-KB-L2-Cache und arbeitet ebenfalls mit der Prozessorkernfrequenz (allerdings mit deutlich höherer Latenz, da er asynchron ist und die Arbeit mit Daten aus den am häufigsten genutzten Bereichen beschleunigen soll Systemspeicher). Somit verfügt der neue Pentium 4 Extreme Edition über einen Gesamt-Cache-Speicher von 2,5 MB! Er ist außerdem der einzige Desktop-Prozessor mit einem in den Kern integrierten Third-Level-Cache.

Der Pentium 4 Extreme Edition-Prozessor wird von Intel hauptsächlich für den Gaming-Markt positioniert, ein Einsatz in produktiven Workstations ist jedoch nicht ausgeschlossen. Der neue Prozessor nutzt einen Kern vom Multiprozessor Xeon MP mit integriertem L3-Cache. Es wurde leicht modifiziert, um einen 800-MHz-Systembus zu unterstützen, den Stromverbrauch zu senken usw. und war in einem Standard-Pentium-4-Gehäuse verpackt.

Beim Verfassen dieses Materials wurden Informationen von Internetseiten verwendet

Alexey Gavrilenko aka [-Alex-]

Pentium (ausgesprochen Pentium) ist eine Marke mehrerer Generationen von Mikroprozessoren der x86-Familie, die seit dem 22. März 1993 von der Intel Corporation hergestellt werden. Der Pentium ist Intels Prozessor der fünften Generation und ersetzt den Intel 80486 (oft einfach als 486 bezeichnet).

Unterschiede zu i3(4)86:

- Adressspeicher hat sich im Vergleich zum Vorgängermodell nicht verändert;

- 64-Bit-Datenkanal (wenn Pentium 32-Bit ist);

- Zum ersten Mal lesen und verarbeiten zwei Pipelines Streams unabhängig voneinander.

- zum ersten Mal kam es zu spekulativen Befehlsausführungen;

- Zum ersten Mal kommt eine Technologie wie die automatische Neuordnung von Befehlen zum Einsatz:

Die geänderte Reihenfolge hat keine Auswirkung. ABER das Problem ist der bedingte Sprung.

ADD AX,BX ADD CX,AX YZ M1 MOV DX, 5h

Lösung: Es wird davon ausgegangen, dass der Übergang abgeschlossen ist und der Befehl daher in die Pipeline eingelesen wurde. Wenn sich herausstellt, dass alles korrekt ist, wird die Ausführung fortgesetzt. Andernfalls wird die Pipeline zurückgesetzt und vom Übergangspunkt aus neu gestartet.

Gründe für die Annahme:

- Übergangsstatistiken (falls viele, mehrere Zyklen);

- Der Vorhersageblock verwendet Statistiken: Wenn der Übergang bedingt ist und zurückzeigt, wird er wahrscheinlich ausgeführt. (Beispiel: wiederholen bis). Und wenn es vorwärts geht, besteht eine hohe Wahrscheinlichkeit, dass es nicht erfüllt wird.

Erstmals Hardware-Unterstützung für Multiprocessing (Verbindung über einen speziellen Bus/spezielle Schnittstelle)

(Datenbus 32 ----> 64, da 2 Förderbänder)

Pentium-Taktrate: 60-150 MHz MMX-Taktrate: 200 MHz

Es gibt zusätzliche Register, die für die Anzahl der Taktzyklen verantwortlich sind, die seit Beginn des Codes vergangen sind.

Es gibt einen Befehl CPUID – CPU-ID.

Alle Arten von Registern.

Architektonisches Merkmal

(vor diesem CISC) In der CISC-Shell gibt es einen internen Transcoder zum Konvertieren von CISC-Befehlen in internen RISC-Code.

Interrupt: Bisher -> PIC (Software-Interrupt-Controller).

Zuvor war die Quelle ein Interrupt-Signal auf dem Prozessorzweig und die Übergangsadresse.

APIC: Quelle – eine Nachricht, die über einen speziellen Bus ankommt.

Intel Pentium P6200-Prozessor

Intel Pentium P6200- Prozessor Einstiegslevel, entworfen für Laptops. Es arbeitet mit 2,13 GHz, unterstützt aber leider nicht die TurboBoost-Technologie automatische Beschleunigung. Außerdem fehlt es an AES-Verschlüsselung und Multithreading-Unterstützung. Die CPU unterstützt die Enhanced Speedstep-Technologie, die den Stromverbrauch in Zeiten geringer Prozessorlast reduziert. Andere Energiespartechnologien sind bei diesem Prozessor (sowie bei der Penryn Pentium-Serie) jedoch deaktiviert.

Der P6200 basiert auf der Arrandale-Mikroarchitektur und verfügt daher über einen integrierten Speichercontroller und Grafikkarte Intel HD Graphics (beide hergestellt in 45 nm). technologischer Prozess, und die CPU ist 32 nm). Die verbaute GMA HD-Grafikkarte arbeitet mit 500 MHz und ist dank Turbo-Boost-Technologie auf 667 MHz übertaktbar.

Die Leistung dieses Prozessors ist aufgrund der niedrigen Taktrate und dem Fehlen von Turbo Boost und Hyperthreading leicht eingeschränkt. Basierend auf der GHz-Taktrate dürfte der Pentium P6200 aufgrund des integrierten Speichercontrollers und kleinerer Kernverbesserungen etwas besser sein als der ähnlich getaktete Core 2 Duo.

*Die angegebenen Taktraten können vom Hersteller geändert werden.Die Geschichte des Pentium-Prozessors

An einem ruhigen Sonntagmorgen am 10. Mai 1992 kamen vier INTEL-Ingenieure am San Jose International Airport an. Nachdem sie die Videoausrüstung aufgebaut hatten, liefen Angela Chang, Eric Devannain, Avtar Saini und Suhel Zaatri nervös durch den Raum und warteten jede Minute auf das Flugzeug aus Oregon.

Als Mark Hopman wenige Minuten nach der Landung des Flugzeugs mit einem kleinen blauen Koffer in der Hand den Korridor verließ, lief die gesamte Begrüßungsgruppe auf ihn zu. Alle Aufmerksamkeit galt dem Koffer, der das Produkt der Entwickler von 5 Oregon Factory enthielt. Es war kaum zu glauben, dass in diesem Koffer das Ergebnis dreijähriger Arbeit vieler Menschen in einem kleinen Chip verkörpert war. Damit begann das Leben des Pentium-Prozessors, der am 22. März 1993 offiziell eingeführt wurde.

Als Vinod Dam im Juni 1989 die ersten Skizzen anfertigte und mit der Entwicklung des Pentium-Prozessors begann, ahnte er noch nicht, dass dieses spezielle Produkt eine der wichtigsten Errungenschaften von INTEL sein würde. Mit dem Aufkommen des Pentium-Prozessors veränderte sich der Computermarkt sofort und eine neue Wettbewerbsphase begann. San Microsistems, MIPS und andere RISC-Prozessorhersteller, die superschnelle Chips entwickeln, haben eindeutig akzeptiert, dass der neue Prozessor von INTEL zum Standard für neue Desktop-PCs werden wird.

Die Geburt des Pentium-Prozessors war nicht einfach

Der Theorie zufolge erstellt das Entwicklungsteam bei der Entwicklung eines Prozessors ein Designkonzept, das seine wichtigsten Eigenschaften und Innovationen definiert. Als nächstes entwerfen Ingenieure die Logik, die dann in spezifische Schaltkreise implementiert wird. Sobald der Schaltungsentwurf abgeschlossen ist, zeichnen Topologiedesigner jeden Transistor. Als Ergebnis ihrer Arbeit entsteht die endgültige Vorlage. In Wirklichkeit war alles anders. Der traditionelle Designprozess wurde radikal umgestaltet, um der Notwendigkeit einer schnelleren Projektabwicklung gerecht zu werden.

Sobald das Entwicklungsteam eine lokale Aufgabe abgeschlossen hatte, verteilten die Manager die Ressourcen neu. Jeder Ingenieur löste ein persönliches Problem. Der Teamgeist wurde ständig durch Verzögerungen und Schwierigkeiten auf die Probe gestellt, der Projektzeitplan wurde dadurch jedoch nicht beeinträchtigt. Bei allen Aufgaben kamen die neuesten Fortschritte im computergestützten Design zum Einsatz. Die beim Entwurf und der Lösung ähnlicher Probleme bei 286-, Intel386- und Intel486-Prozessoren gesammelten Erfahrungen waren sehr nützlich.

Sobald die nächste Phase des Projekts abgeschlossen war, begann sofort der Prozess der umfassenden Tests. Es bestand der Wunsch, die Probleme, die beim Intel486 auftraten, nicht zu wiederholen, was die Einführung in die Produktion verzögerte. Jeder Fehler wurde zurückverfolgt und seine Ursachen beseitigt. Die verbleibenden Ingenieure führten Hunderte von Tests durch, um die Logik, Architektur und das Gesamtdesign zu überprüfen. Sie führten mehr als 5.000 Verfeinerungstests durch, bevor der Pentium-Prozessor seine Architektur fand. Zum Testen wurde eine spezielle Technologie entwickelt, die es ermöglichte, die Funktionsweise eines Pentium-Prozessors mithilfe programmierbarer Geräte zu simulieren, die über Kabel auf 14 Platinen verbunden sind. Erst wenn alle Fehler erkannt wurden, konnte der Prozessor in einem realen System arbeiten. Darüber hinaus beteiligten sich alle großen Entwickler aktiv an der Entwicklung und Erprobung des Pentium-Prozessors persönliche Computer Und Software, was wesentlich zum Gesamterfolg des Projekts beitrug.

Als Ende 1991 der Prozessor-Prototyp fertiggestellt war, konnten Ingenieure darauf Software ausführen. Die Designer begannen, die Verkabelung und den Signalfluss des Substrats unter einem Mikroskop zu untersuchen, um die Topologie zu optimieren und die Betriebseffizienz zu verbessern. Der Entwurf wurde im Februar 1992 weitgehend fertiggestellt. Es begann ein umfassender Test einer Pilotcharge von Prozessoren, bei dem alle Blöcke und Knoten getestet wurden. Im April 1992 wurde beschlossen, dass es an der Zeit sei, mit der kommerziellen Entwicklung des Pentium-Prozessors zu beginnen. Als wichtigster Industriestandort wurde die Oregon Factory 5 ausgewählt.

Mehr als 3 Millionen Transistoren wurden schließlich in Vorlagen übertragen. Die industrielle Entwicklung der Produktion und Feinabstimmung der technischen Eigenschaften begann und endete 10 Monate später, am 22. März 1993, mit einer breiten Präsentation des Pentium-Prozessors.

Moderne Mikroprozessortechnologie von INTEL

Die Fortschritte von INTEL in der Kunst des Halbleiterdesigns und der Halbleiterfertigung ermöglichen die Herstellung leistungsstarker Mikroprozessoren in immer kleineren Gehäusen. Mikroprozessorentwickler arbeiten derzeit mit der Prozesstechnologie „Complementary Metal Oxide Semiconductor“ (CMOS) mit einer Auflösung im Submikrometerbereich.

Durch den Einsatz der Submikron-Technologie können INTEL-Entwickler mehr Transistoren auf jedem Substrat platzieren. Dadurch konnte die Anzahl der Transistoren für die X86-Familie von 29.000 beim 8086-Prozessor auf 1,2 Millionen beim Intel486-DX2-Prozessor erhöht werden, wobei die höchste Leistung beim Pentium-Prozessor erzielt wurde. Es wurde mit 0,8-Mikron-BiCMOS-Technologie hergestellt und enthält 3,1 Millionen Transistoren. Die BiCMOS-Technologie vereint die Vorteile zweier Technologien: Bipolar (Geschwindigkeit) und CMOS (geringer Stromverbrauch). Durch die Verwendung von mehr als doppelt so vielen Transistoren im Pentium-Prozessor im Vergleich zum Intel486 platzierten die Entwickler Komponenten auf dem Substrat, die sich zuvor an der Außenseite des Prozessors befanden. Durch die Integration von Komponenten wird die Zugriffszeit verkürzt, was die Leistung erheblich steigert. Die 0,8-Mikrometer-Technologie von INTEL verwendet dreischichtiges Metall und ist der ursprünglichen 1,0-Mikrometer-zweischichtigen Metalltechnologie, die im Intel486-Prozessor verwendet wurde, überlegen.

INTEL nutzte die neuesten Fortschritte in der Mikroprozessor-Designtechnologie, um Vorteile zu erzielen, die mit alternativen Architekturen in wissenschaftlichen und technischen Workstations vergleichbar sind, und stellte gleichzeitig die Kompatibilität mit Software im Wert von 50 Milliarden US-Dollar sicher, die auf der Mikroprozessorfamilie der X86-Serie basiert.

Und die Software selbst für den Pentium-Prozessor wurde mit neuer Technologie entwickelt. Bereits in der Phase des Entwurfs der Prozessorhardware wurden Experten aller großen Unternehmen, die Betriebssysteme und Compiler entwickeln – Microsoft, IBM, NeXT, Borland, Watcom, MetaWare usw. – in das Projekt einbezogen. Dies ermöglichte die Unterstützung neue Programmiertechnologien auf Hardwareebene unter Berücksichtigung des Corporate Styles der Standardsoftwareanbieter. Andererseits wurden bereits vor der Geburt des neuen Prozessors klassische und spezielle Optimierungsmethoden eingesetzt, um die spezifischen Vorteile der X86-Architektur aufzuzeigen, beispielsweise die Verwendung von Load-Write-Befehlen, leistungsstarke Adressierungsmodi und die Entfernung von invariantem Code Abschnitte aus Schleifen usw. Jetzt ist es allein durch die Neukompilierung herkömmlicher Anwendungen möglich, deren Leistung auf dem neuen Prozessor zu verdoppeln. Dies kann derzeit kein Mitbewerber von INTEL bieten.

Neue Generation von INTEL-Prozessoren

Durch die Kombination von mehr als 3,1 Millionen Transistoren auf einem einzigen Siliziumsubstrat bietet der 32-Bit-Pentium-Prozessor eine hohe Leistung mit Taktraten von 60 und 66 MHz. Seine superskalare Architektur nutzt fortschrittliche Designtechniken, die die Ausführung von mehr als einem Befehl pro Taktzyklus ermöglichen, was dazu führt, dass der Pentium große Mengen PC-kompatibler Software schneller ausführen kann als jeder andere Mikroprozessor. Zusätzlich zu den vorhandenen Softwarefunktionen bietet die leistungsstarke Gleitkomma-Recheneinheit des Pentium-Prozessors eine erhöhte Rechenleistung zur Unterstützung bisher nicht verfügbarer technischer und wissenschaftlicher Anwendungen, die ursprünglich für Workstation-Plattformen entwickelt wurden. So wie lokale Netzwerke und Weitverkehrsnetzwerke weiterhin veraltete hierarchische Netzwerke ersetzen, die von Großrechnern gesteuert werden, sind die Multiprozessor-Vorteile und die Flexibilität des Betriebssystems des Pentium-Prozessors der ideale Host-Computer für die heutigen industriellen Client-Server-Anwendungen.

Da der Pentium-Prozessor in der Lage ist, Leistungsniveaus zu erreichen, die den heutigen High-End-Workstations entsprechen oder diese übertreffen, bietet er Vorteile, die herkömmlichen Workstations fehlen: volle Kompatibilität mit mehr als 50.000 Softwareanwendungen mit einem Aufwand von Milliarden Dollar, die unter der Architektur von INTEL geschrieben wurden. Darüber hinaus unterstützt der Pentium-Prozessor alle wichtigen Betriebssysteme, die auf heutigen Desktops, Workstations und Servern verfügbar sind, einschließlich UNIX, Windows-NT, OS/2, Solaris und NEXTstep.

Pentium-Prozessor. Technische Innovationen

Zahlreiche Innovationen sind ein charakteristisches Merkmal des Pentium-Prozessors in Form einer einzigartigen Kombination aus hoher Leistung, Kompatibilität, Datenintegration und Skalierbarkeit. Das beinhaltet:

- Superskalare Architektur;

- Separates Caching von Programmcode und Daten;

- Korrekter Sprungadressen-Vorhersageblock;

- Hochleistungs-Gleitkomma-Einheit;

- Erweiterter 64-Bit-Datenbus;

- Unterstützung für Multiprozessorbetrieb;

- Mittel zum Einstellen der Speicherseitengröße;

- Tools zur Fehlererkennung und funktionalen Redundanz;

- Leistungsmanagement;

- Skalierbar mit Intel OverDrive-Prozessor.

Pentium-Prozessorarchitektur

1 - 64-Bit-Busschnittstelle;

2 – Programmcode-Caching-Tools;

3 – Puffer vorab abrufen;

4 - 32-Bit-Integer-ALU-Einheit;

5 - 32-Bit-Integer-ALU-Einheit;

6 - Registersatz;

7 – Daten-Caching-Tools;

8 – Block zur Vorhersage der richtigen Übergangsadresse;

9 - Fließkommaberechnungsblock des Förderers.

Superskalare Architektur

Die superskalare Architektur des Pentium-Prozessors ist eine ausschließlich INTEL-basierte Dual-Pipe-Industriearchitektur, die es dem Prozessor ermöglicht, durch die Ausführung von mehr als einem Befehl pro Taktzyklus neue Leistungsniveaus zu erreichen. Der Begriff „superskalar“ bezieht sich auf eine Mikroprozessorarchitektur, die mehr als eine Recheneinheit enthält. Diese Recheneinheiten oder Pipelines sind die Knoten, an denen alle wichtigen Daten- und Befehlsverarbeitungen stattfinden.

Die Entstehung der superskalaren Architektur des Pentium-Prozessors ist eine natürliche Weiterentwicklung der vorherigen Prozessorfamilie mit 32-Bit-Architektur von INTEL. Beispielsweise ist der Intel486-Prozessor in der Lage, mehrere seiner Befehle in einem Taktzyklus auszuführen, frühere INTEL-Prozessorfamilien erforderten jedoch viele Taktzyklen, um einen einzelnen Befehl auszuführen.

Die Möglichkeit, mehrere Befehle in einem einzigen Taktzyklus auszuführen, besteht, weil der Pentium-Prozessor über zwei Pipelines verfügt, die zwei Befehle gleichzeitig ausführen können. Genau wie der Single-Pipe-Intel486 ist auch der Dual-Pipe-Pentium-Prozessor leistungsstark einfacher Befehl in fünf Stufen: Vortraining, erste Dekodierung (Anweisungsdekodierung), zweite Dekodierung (Adressgenerierung), Ausführung und Postback. Dadurch können sich mehrere Befehle in unterschiedlichen Ausführungsstadien befinden, wodurch die Rechenleistung erhöht wird.

Jede Pipeline verfügt über eine eigene Arithmetik-Logik-Einheit (ALU), eine Reihe von Adressgenerierungsgeräten und eine Daten-Caching-Schnittstelle. Wie der Intel486-Prozessor verwendet der Pentium-Prozessor die Befehlsausführung durch Hardware und ersetzt viele der Mikrobefehle, die in früheren Mikroprozessorfamilien verwendet wurden. Zu diesen Anweisungen gehören Lade-, Speicher- und einfache ALU-Operationen, die von der Prozessorhardware ohne Mikrocode ausgeführt werden können. Dies verbessert die Leistung, ohne die Kompatibilität zu beeinträchtigen. Bei der Ausführung komplexerer Befehle werden beide Pipelines der superskalaren Architektur verwendet, um die Ausführungsleistung des erweiterten Mikrocodes des Pentium-Prozessors weiter zu beschleunigen.

Durch diese Architekturinnovationen können im Vergleich zu bisherigen Mikroprozessoren deutlich mehr Befehle in der gleichen Zeit ausgeführt werden.

Getrenntes Caching von Programmcode und Daten

Eine weitere wichtige revolutionäre Verbesserung des Pentium-Prozessors ist die Einführung von Split-Caching. Caching verbessert die Leistung, indem es temporären Speicher für häufig verwendeten Code und aus dem schnellen Speicher abgerufene Daten bereitstellt und für einige Befehle nach Möglichkeit den Zugriff auf den externen Systemspeicher ersetzt. Der Intel486-Prozessor beispielsweise enthält einen einzelnen 8-KB-Block On-Chip-Cache-Speicher, der zum Zwischenspeichern von Programmcode und Daten verwendet wird.

Die Entwickler von INTEL haben diese Einschränkung umgangen, indem sie eine zusätzliche Schaltung verwendet haben, die auf den 3,1 Millionen Transistoren des Pentium-Prozessors basiert (zum Vergleich: der Intel486 enthält 1,2 Millionen Transistoren), wodurch ein separates internes Caching von Programmcode und Daten entsteht. Dies verbessert die Leistung durch Eliminierung von Buskonflikten und macht Dual-Caching häufiger verfügbar als bisher. Zum Beispiel während der Phase vorbereitende Vorbereitung, wird der aus dem Befehlscache erhaltene Befehlscode verwendet. Im Falle eines einzelnen Cache-Blocks kann es zu einem Konflikt zwischen dem Befehlsvorbereitungsprozess und dem Datenzugriff kommen. Durch die getrennte Zwischenspeicherung von Befehlen und Daten werden solche Konflikte vermieden, da beide Befehle gleichzeitig ausgeführt werden können. Die Code- und Datencaches des Pentium-Prozessors enthalten jeweils 8 KB an Informationen und sind jeweils als Satz bidirektionaler Cache-assoziativer Caches organisiert – so konzipiert, dass sie nur das in der Vorschau angegebene 32-Byte-Segment schreiben, schneller als ein externer Cache. Alle diese Leistungsverbesserungen erforderten die Verwendung eines internen 64-Bit-Datenbusses, der Dual-Caching und superskalares Pipelining beim Laden von Downstream-Daten ermöglicht. Der Datencache verfügt über zwei Schnittstellen, eine für jede der Pipelines, sodass er innerhalb eines einzigen Maschinenzyklus Daten an zwei separate Anweisungen bereitstellen kann. Nachdem Daten aus dem Cache abgerufen wurden, werden sie im Rückschreibmodus in den Hauptspeicher geschrieben. Diese Caching-Technik gibt bessere Leistung als einfaches Direct-Write-Caching, bei dem der Prozessor Daten gleichzeitig in den Cache und den Hauptspeicher schreibt. Der Pentium-Prozessor ist jedoch in der Lage, sich dynamisch so zu konfigurieren, dass er nur Schreib-Caching unterstützt.

Daher werden beim Daten-Caching zwei verschiedene großartige Lösungen verwendet: ein Write-Back-Cache und ein Algorithmus namens MESI-Protokoll (Modify, Exclude, Allocate, Deallocate). Mit dem Write-Back-Cache können Sie im Gegensatz zum bisher verwendeten direkten einfachen Caching in den Cache schreiben, ohne auf den Hauptspeicher zuzugreifen.

Diese Lösungen steigern die Produktivität, indem sie einen neu gestalteten Bus verwenden und den Engpass im System proaktiv beseitigen. Das MESI-Protokoll wiederum ermöglicht Daten im Cache-Speicher und Externer Speicher match ist eine hervorragende Lösung in fortschrittlichen Multiprozessorsystemen, in denen verschiedene Prozessoren möglicherweise dieselben Daten teilen.

Hochleistungs-Gleitkommaeinheit

Die steigende Flut an 32-Bit-Softwareanwendungen umfasst viele rechenintensive, grafikbasierte Programme, die viele CPU-Ressourcen verbrauchen, um Gleitkommaoperationen durchzuführen, die mathematische Berechnungen durchführen. Da die Anforderungen, die Gleitkommasoftware an Personalcomputer stellt, ständig steigen, können Verbesserungen in der Mikroprozessortechnologie diesen Anforderungen gerecht werden. Der Intel486 DX-Prozessor beispielsweise war der erste Mikroprozessor, der auf demselben Substrat mit einem mathematischen Coprozessor integriert war. Frühere Familien von INTEL-Prozessoren verwendeten einen externen mathematischen Coprozessor, wenn Gleitkommaberechnungen erforderlich waren.

Der Pentium-Prozessor ermöglicht mathematische Berechnungen auf höherer Ebene durch die Verwendung einer fortschrittlichen integrierten Gleitkommaeinheit, die eine Acht-Zyklus-Pipeline und hardwarebasierte mathematische Kernfunktionen umfasst. Gleitkomma-Befehlspipelines mit vier Zyklen ergänzen die Ganzzahlpipeline mit vier Zyklen. Die meisten Gleitkommaanweisungen können in einer einzelnen Integer-Pipeline ausgeführt und dann in die Gleitkomma-Pipeline eingespeist werden. Gängige Gleitkommafunktionen wie Addition, Multiplikation und Division sind in Hardware implementiert, um Berechnungen zu beschleunigen.

Aufgrund dieser Innovationen führt der Pentium-Prozessor Gleitkommabefehle fünfmal schneller aus als der 33-MHz-Intel486 DX und optimiert sie so für numerische Hochgeschwindigkeitsberechnungen, die für fortgeschrittene Videoanwendungen wie CAD und 3D-Grafiken unerlässlich sind.

Der 66-MHz-Pentium-Prozessor schneidet mit einer SPECint92-Bewertung von 64,5 wie ein Zahlenknacker ab, fast so gut wie der Alpha RISC-Prozessor von Digital, taktet aber doppelt so schnell.

Die Gesamtleistung des Pentium-Prozessors ist sechsmal höher als die des 25-MHz-Intel486-SX und 2,6-mal höher als die des 66-MHz-Intel486-DX2. Der iCOMP-Bewertungsindex für einen 66-MHz-Pentium-Prozessor, der 112 Millionen Operationen pro Sekunde ausführt, beträgt 567. Der iCOMP-Index (Intel COmparative Microprocessor Peformance) führt einen relativen Vergleich der Leistung von 32-Bit-Prozessoren von INTEL durch.

Erweiterter 64-Bit-Datenbus

Der Pentium-Prozessor ist von außen ein 32-Bit-Gerät. Der externe Datenbus zum Speicher ist 64-Bit, wodurch sich die pro Buszyklus übertragene Datenmenge verdoppelt. Der Pentium-Prozessor unterstützt mehrere Arten von Buszyklen, einschließlich des Burst-Modus, der Daten von 256 Bit in den Datencache und innerhalb eines einzigen Buszyklus überträgt.

Der Datenbus ist die Hauptstraße, die Informationen zwischen dem Prozessor und dem Speichersubsystem überträgt. Dank dieses 64-Bit-Datenbusses verbessert der Pentium-Prozessor die Übertragungsgeschwindigkeiten gegenüber dem Intel486-DX-Prozessor deutlich – 528 MB/s beim 66-MHz-Prozessor im Vergleich zu 160 MB/s beim 50-MHz-Intel486-DX-Prozessor. Dieser verbesserte Datenbus erleichtert Hochgeschwindigkeitsrechnen, indem er die gleichzeitige Befehls- und Datenzufuhr der superskalaren Verarbeitungseinheit unterstützt und so eine noch höhere Gesamtleistung des Pentium-Prozessors als der Intel486 DX-Prozessor liefert.

Da der Pentium-Prozessor über einen breiteren Datenbus verfügt, bietet er im Allgemeinen eine Pipeline-Verteilung der Buszyklen, was zu einer Erhöhung des Busdurchsatzes beiträgt. Durch das Pipelining von Buszyklen kann der zweite Zyklus beginnen, bevor die Ausführung des ersten Zyklus abgeschlossen ist. Dies gibt dem Speichersubsystem mehr Zeit zum Dekodieren der Adresse, was die Verwendung langsamerer, kostengünstigerer Speicherkomponenten ermöglicht, was zu geringeren Gesamtsystemkosten führt. Die Beschleunigung von Lese- und Schreibprozessen, die Adress- und Datenparallelität sowie die Single-Cycle-Decodierung sorgen in Kombination für einen verbesserten Durchsatz und eine Verbesserung der Systemfunktionen.

Mehrfachverarbeitung

Der Pentium-Prozessor ist ideal für die zunehmende Welle von Multiprozessorsystemen und bietet das höchste Maß an Leistung und Rechenleistung im modernen Computing. Multiprozessoranwendungen, die zwei oder mehr Pentium-Prozessoren verbinden, werden durch fortschrittliche Siliziumarchitekturen, separates On-Chip-Code- und Daten-Caching, Chipsätze für die externe Cache-Verwaltung und ausgefeilte Datenintegritätskontrollen gut unterstützt.

Wie bereits erwähnt, unterstützt der Pentium-Prozessor mit seinem MESI-Protokoll den Cache-geordneten Cache. Wenn ein Prozessor auf Daten zugreift, die in einem anderen Prozessor zwischengespeichert sind, kann er die richtigen Daten empfangen. Und wenn die Daten geändert wurden, haben alle Auftragsverarbeiter Zugriff darauf, die Daten in geänderter Form zu erhalten. Welche Befehle das System erkennt, bestimmt der neueste Pentium-Prozessor von INTEL auch anhand der verwendeten Programmiermethode. Dadurch erfahren Sie ganz konkret, wie Software, die für ein Einprozessorsystem entwickelt wurde, in einer Mehrprozessorumgebung korrekt funktionieren kann.

Mittel zur Aufteilung des Speichers in Seiten

Der Pentium-Prozessor bietet Optionen zur Unterstützung aller herkömmlichen Speicherseitengrößen – 4 KB oder mehr, 4 MB-Seiten. Mit dieser Option können Sie die Häufigkeit des Seitenwechsels im Komplex berechnen Grafikanwendungen, Framebuffer und Kernel Betriebssysteme, wobei die vergrößerte Seitengröße es Benutzern nun ermöglicht, anfangs unhandliche Objekte breiter zu verkleinern. Mehr Seiten führen zu einer höheren Leistung, was sich in der Anwendungssoftware widerspiegelt.

Fehlererkennung und funktionale Redundanz