प्रोसेसर परिवार इंटेल पेंटियम

- P54CS

- तिलमुक

पेंटियम(उच्चारण पेंटियम) - ट्रेडमार्क 22 मार्च 1993 से इंटेल कॉर्पोरेशन द्वारा निर्मित x86 परिवार के माइक्रोप्रोसेसरों की कई पीढ़ियाँ। पेंटियम इंटेल का पांचवीं पीढ़ी का प्रोसेसर है और इंटेल 80486 (अक्सर इसे 486 के रूप में संदर्भित) की जगह लेता है।

कहानी

मॉडल

प्रारंभ में (22 मार्च, 1993), 60 और 66 मेगाहर्ट्ज की आवृत्तियों के साथ पी5 कोर पर आधारित केवल दो मॉडल प्रस्तुत किए गए थे। बाद में, बेहतर कोर के आधार पर अधिक शक्तिशाली पेंटियम प्रोसेसर जारी किए गए। इसके अलावा, प्रोसेसर और पेंटियम ओवरड्राइव प्रोसेसर के मोबाइल संस्करण प्रस्तुत किए गए।

| कर्नेल कोडनेम | पी 5 | पी54सी | P54CS | पी55सी | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| तकनीकी प्रक्रिया, एनएम | 800 | 600 | 350 | ||||||||||

| कोर घड़ी आवृत्ति, मेगाहर्ट्ज | 60 | 66 | 75 | 90 | 100 | 120 | 133 | 150 | 166 | 200 | 166 | 200 | 233 |

| की घोषणा की | 23 मार्च 1993 | 10 अक्टूबर 1993 | 7 मार्च 1994 | 27 मार्च 1995 | 12 जून 1995 | 4 जनवरी 1996 | 10 जून 1996 | 8 जनवरी 1997 | 2 जून 1997 | ||||

पी 5

60 और 66 मेगाहर्ट्ज की कोर क्लॉक स्पीड वाले पहली पीढ़ी के पेंटियम प्रोसेसर के केवल दो मॉडल की घोषणा 23 मार्च 1993 को की गई थी।

प्रोसेसर को 273-पिन सीपीजीए पैकेज में तैयार किया गया था, इसे सॉकेट 4 प्रोसेसर सॉकेट में मदरबोर्ड पर स्थापित किया गया था और इसके लिए 5 वी बिजली की आपूर्ति की आवश्यकता थी। सिस्टम बस (एफएसबी) आवृत्ति कोर आवृत्ति के बराबर थी गुणक 1.0 के बराबर था.

सभी पेंटियम प्रोसेसर एसएल एन्हांस्ड वर्ग से संबंधित हैं - इसका मतलब है कि उनके पास एक एसएमएम प्रणाली है जो बिजली की खपत को कम करती है। दूसरे स्तर का कैश मदरबोर्ड पर स्थित था और इसका आकार 1 एमबी तक हो सकता था। 60-100 मेगाहर्ट्ज (पी5 और पी54सी कोर) की आवृत्तियों वाले प्रोसेसर के शुरुआती संस्करणों में गणित कोप्रोसेसर मॉड्यूल में एक बग था, जिसके कारण दुर्लभ मामलों में डिवीजन ऑपरेशन की सटीकता में कमी आई। यह दोष 1994 में खोजा गया और इसे "पेंटियम FDIV बग" के रूप में जाना जाने लगा।

P5 कोर पर आधारित प्रोसेसर का निर्माण द्विध्रुवी BiCMOS प्रौद्योगिकी का उपयोग करके 800-नैनोमीटर प्रक्रिया प्रौद्योगिकी का उपयोग करके किया गया था। प्रोसेसर में 3.1 मिलियन ट्रांजिस्टर हैं, और कोर डाई का आकार 294 मिमी² है। पेंटियम 66 3.2 ए की विद्युत धारा की खपत करता है और इसकी शक्ति 16 डब्ल्यू है, जिसके लिए एक अतिरिक्त पंखे की स्थापना की आवश्यकता होती है। ऐसे प्रोसेसर का उत्पादन बहुत कठिन हो गया और प्रयोग करने योग्य क्रिस्टल का प्रतिशत बहुत छोटा हो गया। कई विशेषज्ञों ने पहली पीढ़ी के पेंटियम प्रोसेसर की कई कमियों (देखें: F0 0f c7 c8) की ओर इशारा करते हुए इन मॉडलों को खरीदने की सलाह नहीं दी। कुछ देर के लिए प्रोडक्शन रोकना पड़ा. हालाँकि, P54C कोर पर आधारित बेहतर प्रोसेसर का उत्पादन जल्द ही शुरू हो गया।

पी54सी

दूसरी पीढ़ी के पेंटियम प्रोसेसर घड़ी गुणन का उपयोग करते हैं और सिस्टम बस से तेज़ होते हैं। एक गुणक का उपयोग यह इंगित करने के लिए किया जाता है कि प्रोसेसर कोर घड़ी आवृत्ति सिस्टम बस आवृत्ति से कितनी गुना अधिक है। P54C कोर पर आधारित सभी प्रोसेसर में गुणक 1.5 है।

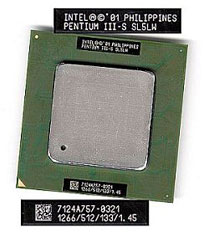

P54CS

इस कोर पर आधारित पहला प्रोसेसर 27 मार्च 1995 को जारी किया गया था। संक्षेप में, यह कोर एक P54C कोर है जिसे 350 एनएम द्विध्रुवी BiCMOS तकनीक का उपयोग करके निर्मित किया गया है, जिससे कोर डाई आकार को 91 मिमी² (पेंटियम 120 और 133 प्रोसेसर) तक कम करना संभव हो गया, लेकिन जल्द ही, कोर अनुकूलन के परिणामस्वरूप, इसका आकार ट्रांजिस्टर की समान संख्या के साथ इसे 83 मिमी² तक घटा दिया गया। उसी समय, पेंटियम 200 ने 4.6 ए की धारा की खपत की, और इसकी अधिकतम ऊर्जा अपव्यय (गर्मी अपव्यय) 15.5 डब्ल्यू थी।

पी55सी

8 जनवरी 1997 को, तीसरी पीढ़ी के P5 कोर (P55C) पर आधारित पेंटियम प्रोसेसर जारी किए गए। हाइफ़ा (इज़राइल) में इंटेल आर एंड डी सेंटर ने P55C कोर में निर्देशों का एक नया सेट जोड़ा, जिसे एमएमएक्स (मल्टीमीडिया एक्सटेंशन) कहा जाता है, जो मल्टीमीडिया अनुप्रयोगों में कंप्यूटर के प्रदर्शन को उल्लेखनीय रूप से (अनुकूलन के आधार पर 10 से 60% तक) बढ़ाता है। परिणामस्वरूप, इन प्रोसेसरों को पेंटियम w/MMX तकनीक कहा जाता है (आमतौर पर इसे पेंटियम MMX के रूप में संक्षिप्त किया जाता है)। नए प्रोसेसर में पाइपलाइन इंस्ट्रक्शन प्रोसेसिंग के साथ एक एमएमएक्स डिवाइस शामिल है, एल1 कैश को 32 केबी (डेटा के लिए 16 केबी और निर्देशों के लिए 16 केबी) तक बढ़ाया गया है। के होते हैं नया प्रोसेसर 4.5 मिलियन ट्रांजिस्टर का और सिलिकॉन सेमीकंडक्टर्स का उपयोग करके उन्नत 280-नैनोमीटर सीएमओएस तकनीक का उपयोग करके उत्पादित किया जाता है, जो 2.8 वी के वोल्टेज पर संचालित होता है। अधिकतम वर्तमान खपत 6.5 ए है, गर्मी अपव्यय 17 डब्ल्यू है (पेंटियम 233 एमएमएक्स के लिए)। पेंटियम एमएमएक्स प्रोसेसर का क्रिस्टल क्षेत्र 141 मिमी² है। प्रोसेसर सॉकेट 7 के लिए 296-पिन सीपीजीए या पीपीजीए पैकेज में तैयार किए गए थे।

पेंटियम ओवरड्राइव

पेंटियम ओवरड्राइव की कई पीढ़ियाँ जारी की गईं।

- 1995 में, पहला पेंटियम ओवरड्राइव (P24T कोर पर) जारी किया गया था। इसे सॉकेट 2 या सॉकेट 3 सॉकेट में इंस्टॉलेशन के लिए डिज़ाइन किया गया था और यह 5 वी की आपूर्ति वोल्टेज के साथ काम करता था, यानी, इसका उपयोग मदरबोर्ड को बदले बिना 486 प्रोसेसर का उपयोग करके सिस्टम को अपग्रेड करने के लिए किया गया था। इसके अलावा, इस प्रोसेसर में सभी फ़ंक्शन थे पेंटियम प्रोसेसरपहली पीढ़ी (P5 कोर पर)। दो मॉडल जारी किए गए, जो 63 और 83 मेगाहर्ट्ज की आवृत्तियों पर काम कर रहे थे, पुराने ने 2.8 ए की वर्तमान खपत की और 14 डब्ल्यू की बिजली अपव्यय की थी। अधिक लागत के कारण यह प्रोसेसर सामने आने से पहले ही चलन से बाहर हो गया। और यद्यपि कुछ समय बाद (4 मार्च, 1996) इन प्रोसेसरों को पी5टी कोर (अनिवार्य रूप से एक पी54सीएस कोर) पर आधारित 120 और 133 मेगाहर्ट्ज की आवृत्तियों के साथ पेंटियम ओडीपी5वी द्वारा प्रतिस्थापित कर दिया गया, वे भी लोकप्रिय नहीं हुए।

- 4 मार्च 1996 को, P54CT कोर पर आधारित पेंटियम ओवरड्राइव का अगला संस्करण - पेंटियम ODP3V - जारी किया गया। यह कोर P54CS कोर पर आधारित है। प्रोसेसर को सॉकेट 5 या सॉकेट 7 के लिए 320-पिन सीपीजीए पैकेज में तैयार किया गया था।

- 3 मार्च 1997 को, P54CTB कोर (P55C के अनुरूप) पर निर्मित दो पेंटियम ODPMT मॉडल (150 और 166 मेगाहर्ट्ज की आवृत्तियों के साथ) जारी किए गए थे। बाद में, 4 अगस्त 1997 को, एक ही कोर पर (180 और 200 मेगाहर्ट्ज की आवृत्तियों के साथ) दो और मॉडल जारी किए गए। वे 320-पिन सीपीजीए पैकेज में उत्पादित किए गए थे और सॉकेट 5 या सॉकेट 7 (पेंटियम ओडीपीएमटी-200 एमएमएक्स - सॉकेट 7 केवल) के लिए डिज़ाइन किए गए थे।

तिलमुक

इस कोर पर आधारित प्रोसेसर लैपटॉप कंप्यूटर के लिए अभिप्रेत थे और तथाकथित रूप से उपयोग किए जाते थे। 280 पिन वाले "मोबाइल मॉड्यूल" एमएमसी-1 मोबाइल मॉड्यूल कनेक्टर के साथ मिलकर काम किया इंटेल चिपसेट 430 TX और मदरबोर्ड पर 512 KB कैश मेमोरी है। टिलमूक कोर (ओरेगॉन, संयुक्त राज्य अमेरिका में एक शहर के नाम पर) एक कम वोल्टेज वाला P55C कोर है - 300 मेगाहर्ट्ज मॉडल 2.0 V पर संचालित होता है, जो 4.5 A की खपत करता है और 8,4 W का अपव्यय करता है। पुराने मॉडल (233, 266 और 300 मेगाहर्ट्ज की आवृत्ति के साथ) 250 एनएम प्रक्रिया प्रौद्योगिकी का उपयोग करके तैयार किए गए थे और उनका क्रिस्टल क्षेत्र 90 मिमी² था, 166 मेगाहर्ट्ज कोर आवृत्ति वाले संस्करण भी तैयार किए गए थे अगस्त 1997 से, मॉडल 266 जनवरी 1998 से, और लाइन में शीर्ष मॉडल जनवरी 1999 में पेश किया गया था।

(जिसे अक्सर केवल 486 कहा जाता है)।

विश्वकोश यूट्यूब

1 / 4

पेंटियम 2 कार्ड पर क्यों थे? | नॉस्टेल्जिया नर्ड

पेंटियम बनाम 486 पीसी (1993)

एक सीपीयू पेंटियम 4 का उपयोग करना और एक सूचनात्मक अध्ययन का अभ्यास करना।

पेंटियम 486 को क्यों मारता है (पाइपलाइन और कैश) | पुरानी यादों वाला बेवकूफ

उपशीर्षक

कहानी

P5 कोर पर आधारित प्रोसेसर का निर्माण द्विध्रुवी BiCMOS प्रौद्योगिकी का उपयोग करके 800-नैनोमीटर प्रक्रिया प्रौद्योगिकी का उपयोग करके किया गया था। प्रोसेसर में 3.1 मिलियन ट्रांजिस्टर हैं, और कोर डाई का आकार 294 मिमी² है। पेंटियम 66 3.2 ए की विद्युत धारा की खपत करता है और इसकी शक्ति 16 डब्ल्यू है, जिसके लिए एक अतिरिक्त पंखे की स्थापना की आवश्यकता होती है। ऐसे प्रोसेसर का उत्पादन बहुत कठिन हो गया और प्रयोग करने योग्य क्रिस्टल का प्रतिशत बहुत छोटा हो गया। कई विशेषज्ञों ने पहली पीढ़ी के पेंटियम प्रोसेसर की कई कमियों (देखें: F0 0f c7 c8) की ओर इशारा करते हुए इन मॉडलों को खरीदने की सलाह नहीं दी। कुछ देर के लिए प्रोडक्शन रोकना पड़ा. हालाँकि, P54C कोर पर आधारित बेहतर प्रोसेसर का उत्पादन जल्द ही शुरू हो गया।

पी54सी

दूसरी पीढ़ी के पेंटियम प्रोसेसर घड़ी गुणन का उपयोग करते हैं और सिस्टम बस से तेज़ होते हैं। एक गुणक का उपयोग यह इंगित करने के लिए किया जाता है कि प्रोसेसर कोर घड़ी आवृत्ति सिस्टम बस आवृत्ति से कितनी गुना अधिक है। P54C कोर पर आधारित सभी प्रोसेसर में गुणक 1.5 है।

P54CS

इस कोर पर आधारित पहला प्रोसेसर 27 मार्च 1995 को जारी किया गया था। संक्षेप में, यह कोर एक P54C कोर है जिसे 350 एनएम द्विध्रुवी BiCMOS तकनीक का उपयोग करके निर्मित किया गया है, जिससे कोर डाई आकार को 91 मिमी² (पेंटियम 120 और 133 प्रोसेसर) तक कम करना संभव हो गया, लेकिन जल्द ही, कोर अनुकूलन के परिणामस्वरूप, इसका आकार ट्रांजिस्टर की समान संख्या के साथ इसे 83 मिमी² तक घटा दिया गया। उसी समय, पेंटियम 200 ने 4.6 ए की धारा की खपत की, और इसकी अधिकतम ऊर्जा अपव्यय (गर्मी अपव्यय) 15.5 डब्ल्यू थी।

पी55सी

8 जनवरी 1997 को, तीसरी पीढ़ी के P5 कोर (P55C) पर आधारित पेंटियम प्रोसेसर जारी किए गए। हाइफ़ा (इज़राइल) में इंटेल आर एंड डी सेंटर ने P55C कोर में निर्देशों का एक नया सेट जोड़ा, जिसे एमएमएक्स (मल्टीमीडिया एक्सटेंशन) कहा जाता है, जो मल्टीमीडिया अनुप्रयोगों में कंप्यूटर के प्रदर्शन को उल्लेखनीय रूप से (अनुकूलन के आधार पर 10 से 60% तक) बढ़ाता है। परिणामस्वरूप, इन प्रोसेसरों को पेंटियम w/MMX तकनीक कहा जाता है (आमतौर पर इसे पेंटियम MMX तक छोटा किया जाता है)। नए प्रोसेसर में पाइपलाइन इंस्ट्रक्शन प्रोसेसिंग के साथ एक एमएमएक्स डिवाइस शामिल है, एल1 कैश को 32 केबी (डेटा के लिए 16 केबी और निर्देशों के लिए 16 केबी) तक बढ़ाया गया है। नए प्रोसेसर में 4.5 मिलियन ट्रांजिस्टर होते हैं और इसे सिलिकॉन सेमीकंडक्टर्स का उपयोग करके उन्नत 280-नैनोमीटर सीएमओएस तकनीक का उपयोग करके निर्मित किया जाता है, जो 2.8 वी के वोल्टेज पर संचालित होता है। अधिकतम वर्तमान खपत 6.5 ए है, गर्मी अपव्यय 17 डब्ल्यू है (पेंटियम 233 एमएमएक्स के लिए)। पेंटियम एमएमएक्स प्रोसेसर का क्रिस्टल क्षेत्र 141 मिमी² है। प्रोसेसर सॉकेट 7 के लिए 296-पिन सीपीजीए या पीपीजीए पैकेज में तैयार किए गए थे।

पेंटियम ओवरड्राइव

पेंटियम ओवरड्राइव की कई पीढ़ियाँ जारी की गईं।

- 1995 में, पहला पेंटियम ओवरड्राइव (P24T कोर पर) जारी किया गया था। इसे सॉकेट 2 या सॉकेट 3 प्रकार के सॉकेट में इंस्टॉलेशन के लिए डिज़ाइन किया गया था और यह 5 वी की आपूर्ति वोल्टेज के साथ काम करता था, यानी, इसका उपयोग मदरबोर्ड को बदले बिना 486 प्रोसेसर का उपयोग करके सिस्टम को अपग्रेड करने के लिए किया गया था। इसके अलावा, इस प्रोसेसर में पहली पीढ़ी के पेंटियम प्रोसेसर (पी5 कोर पर) के सभी कार्य थे। दो मॉडल जारी किए गए, जो 63 और 83 मेगाहर्ट्ज की आवृत्तियों पर काम कर रहे थे, पुराने ने 2.8 ए की वर्तमान खपत की और 14 डब्ल्यू की बिजली अपव्यय की थी। अधिक लागत के कारण यह प्रोसेसर सामने आने से पहले ही चलन से बाहर हो गया। और यद्यपि कुछ समय बाद (4 मार्च, 1996) इन प्रोसेसरों को पी5टी कोर (अनिवार्य रूप से एक पी54सीएस कोर) पर आधारित 120 और 133 मेगाहर्ट्ज की आवृत्तियों के साथ पेंटियम ओडीपी5वी द्वारा प्रतिस्थापित कर दिया गया, वे भी लोकप्रिय नहीं हुए।

- 4 मार्च 1996 को, P54CT कोर पर आधारित पेंटियम ओवरड्राइव का अगला संस्करण - पेंटियम ODP3V - जारी किया गया। यह कोर P54CS कोर पर आधारित है। प्रोसेसर को सॉकेट 5 या सॉकेट 7 के लिए 320-पिन सीपीजीए पैकेज में तैयार किया गया था।

- 3 मार्च 1997 को, P54CTB कोर (P55C के अनुरूप) पर निर्मित दो पेंटियम ODPMT मॉडल (150 और 166 मेगाहर्ट्ज की आवृत्तियों के साथ) जारी किए गए थे। बाद में, 4 अगस्त 1997 को, एक ही कोर पर (180 और 200 मेगाहर्ट्ज की आवृत्तियों के साथ) दो और मॉडल जारी किए गए। वे 320-पिन सीपीजीए पैकेज में उत्पादित किए गए थे और सॉकेट 5 या सॉकेट 7 (पेंटियम ओडीपीएमटी-200 एमएमएक्स - सॉकेट 7 केवल) के लिए डिज़ाइन किए गए थे।

तिलमुक

इस कोर पर आधारित प्रोसेसर लैपटॉप कंप्यूटर के लिए अभिप्रेत थे और तथाकथित रूप से उपयोग किए जाते थे। 280 पिन वाला "मोबाइल मॉड्यूल" एमएमसी-1 मोबाइल मॉड्यूल कनेक्टर इंटेल 430 टीएक्स चिपसेट के साथ मिलकर काम करता था और मदरबोर्ड पर 512 केबी कैश मेमोरी थी। टिलमूक कोर (ओरेगॉन, संयुक्त राज्य अमेरिका में एक शहर के नाम पर) एक कम वोल्टेज वाला P55C कोर है - 300 मेगाहर्ट्ज मॉडल 2.0 V पर संचालित होता है, जो 4.5 A की खपत करता है और 8,4 W का अपव्यय करता है। पुराने मॉडल (233, 266 और 300 मेगाहर्ट्ज की आवृत्ति के साथ) 250 एनएम प्रक्रिया प्रौद्योगिकी का उपयोग करके तैयार किए गए थे और उनका क्रिस्टल क्षेत्र 90 मिमी² था, 166 मेगाहर्ट्ज कोर आवृत्ति वाले संस्करण भी तैयार किए गए थे अगस्त 1997 से, मॉडल 266 जनवरी 1998 से, और लाइन में शीर्ष मॉडल जनवरी 1999 में पेश किया गया था।

अपने अस्तित्व के केवल 10 वर्षों में, इंटेल के पेंटियम प्रोसेसर ने एक लंबा सफर तय किया है। अकेले घड़ी की आवृत्ति 60 मेगाहर्ट्ज से 3200 मेगाहर्ट्ज तक 53 गुना से अधिक बढ़ गई है। इंटेल कई विकासों का लेखक भी है, जिनका उपयोग बाद में एएमडी और वीआईए जैसी कंपनियों द्वारा किया गया।

केवल इन 10 वर्षों में, निम्नलिखित प्रोसेसर परिवार जारी किए गए:

- 1993 - इंटेल पेंटियम

- 1995 - इंटेल पेंटियम प्रो

- 1997 - इंटेल पेंटियम एमएमएक्स

- 1997 - इंटेल पेंटियम II

- 1999 - इंटेल पेंटियम!!!

- 2000 - इंटेल पेंटियम 4

आइए अब उनमें से प्रत्येक को अधिक विस्तार से देखें।

यह सब 22 मार्च 1993 को शुरू हुआ। यह तब था जब इंटेल ने ब्रांड के तहत पहला प्रोसेसर पेश किया था पेंटियम, जो कई वर्षों तक वर्ड प्रोसेसर का पर्याय बन गया।

यह डुअल-पाइप संरचना वाला पहला प्रोसेसर था। एक कोड नाम था पी 5. था घड़ी की गति 60 और 66 मेगाहर्ट्ज। बस आवृत्ति प्रोसेसर घड़ी आवृत्ति के साथ मेल खाती है। प्रोसेसर में 3.1 मिलियन से अधिक ट्रांजिस्टर थे और 0.80 माइक्रोन तकनीक का उपयोग करके उत्पादित किए गए थे, और बाद में - 0.60 माइक्रोन। प्रथम स्तर L1 कैश का आकार 16 KB था - डेटा के लिए 8 KB और निर्देशों के लिए 8 KB, जबकि दूसरे स्तर का कैश मदरबोर्ड पर स्थित था और इसका वॉल्यूम 1 MB तक हो सकता था। प्रोसेसर सॉकेट 4 कनेक्टर के लिए तैयार किया गया था।

एक साल बाद, मार्च 1994 में, इंटेल ने दूसरी पीढ़ी का पेंटियम (कोर) जारी किया पी54).

प्रोसेसर की आवृत्ति 75 से 200 मेगाहर्ट्ज तक थी। बस आवृत्ति 50-66 मेगाहर्ट्ज। L1 कैश का आकार वही रहता है - 16 KB (डेटा के लिए 8 KB और निर्देशों के लिए 8 KB)। दूसरे स्तर का कैश मदरबोर्ड पर रहता था और इसका वॉल्यूम 1 एमबी तक हो सकता था। इस प्रोसेसर का उत्पादन करते समय, इंटेल अधिक उन्नत 0.50 माइक्रोन प्रक्रिया प्रौद्योगिकी का उपयोग करता है। प्रोसेसर में 3.3 मिलियन से अधिक ट्रांजिस्टर थे। सॉकेट 5, बाद में सॉकेट 7 के लिए निर्मित।

पेंटियम प्रो

1 नवंबर 1995, पेंटियम प्रो प्रोसेसर (कोडनेम) के रिलीज के साथ पी 6), छठी पीढ़ी के प्रोसेसर की उलटी गिनती शुरू हो गई है। वे गतिशील निष्पादन तकनीक के उपयोग से पिछली पीढ़ी से अलग थे - निर्देश निष्पादन के क्रम में परिवर्तन और एक डबल स्वतंत्र बस की वास्तुकला। एक और बस जोड़ी गई है जो प्रोसेसर को दूसरे स्तर के कैश से जोड़ती है, जो कोर में बनाया गया है। परिणामस्वरूप, प्रोसेसर आवृत्ति पर काम करते हुए पहली बार L2 कैश का उपयोग किया गया। L2 कैश का प्रारंभिक आकार 256 KB है; 18 अगस्त 1997 तक यह 1024 केबी तक पहुंच गया। अधिकतम आकार 2048 KB है. प्रथम स्तर का कैश वही रहता है: 8 KB + 8 KB। इसकी क्लॉक फ्रीक्वेंसी 150, 166, 180, 200 मेगाहर्ट्ज थी।

पेंटियम प्रो प्रोसेसर को पिन ऐरे के साथ SPGA (स्टैगर्ड पिन ग्रिड ऐरे) पैकेज में तैयार किया गया था। एक मामले में दो क्रिस्टल स्थापित किए गए थे - एक प्रोसेसर कोर और एक स्व-निर्मित दूसरे स्तर का कैश। सममित मल्टीप्रोसेसिंग के लिए 4 प्रोसेसर तक संयोजित करने की क्षमता के साथ सॉकेट 8 में स्थापित। बस 60-66 मेगाहर्ट्ज। 32-बिट कंप्यूटिंग और मल्टीटास्किंग में, इसने पेंटियम से काफी बेहतर प्रदर्शन किया, लेकिन 16-बिट अनुप्रयोगों में यह उससे कमतर था। 150 मेगाहर्ट्ज प्रोसेसर का उत्पादन 0.60 माइक्रोन प्रक्रिया प्रौद्योगिकी, पुराने मॉडल - 0.35 माइक्रोन का उपयोग करके किया गया था। पेंटियम PRO में 5.5 मिलियन से अधिक ट्रांजिस्टर शामिल थे, साथ ही 15.5 से 31 मिलियन तक कैश शामिल था। पेंटियम एमएमएक्स

प्रोसेसर 8 जनवरी 1997 को जारी किया गया था पेंटियम w/MMX प्रौद्योगिकी(कोड नाम पी55), जो पेंटियम लाइन की निरंतरता है, जिसमें 57 एमएमएक्स (मल्टी मीडिया एक्सटेंशन) कमांड का एक नया सेट पहली बार लागू किया गया था, जिससे मल्टीमीडिया अनुप्रयोगों में कंप्यूटर प्रदर्शन में उल्लेखनीय वृद्धि हुई (अनुकूलन के आधार पर 10 से 60% तक)।

इसका उत्पादन 166, 200 और 233 मेगाहर्ट्ज की घड़ी आवृत्तियों के साथ किया गया था। 66 मेगाहर्ट्ज बस पर काम किया। पेंटियम की तुलना में, प्रथम स्तर के कैश का आकार दोगुना कर दिया गया, जिसकी मात्रा 32 KB थी। पिछले संस्करणों की तरह, एक अलग कैश का उपयोग किया गया था: डेटा के लिए 16 केबी और निर्देशों के लिए 16 केबी। यह कहने योग्य है कि L1 कैश का यह विभाजन (और आकार) कई वर्षों से एक प्रकार का मानक बन गया है। दूसरे स्तर का कैश, अपने पूर्ववर्ती की तरह, मदरबोर्ड पर बना रहा और इसकी मात्रा 1 एमबी तक हो सकती है। प्रोसेसर 0.35 माइक्रोन तकनीक का उपयोग करके निर्मित किए गए थे और इसमें 4.5 मिलियन ट्रांजिस्टर शामिल थे। सॉकेट 7 के लिए डिज़ाइन किया गया।

पेंटियम II

पेंटियम II नामक पहला प्रोसेसर 7 मई 1997 को सामने आया। ये प्रोसेसर पेंटियम प्रो आर्किटेक्चर और एमएमएक्स तकनीक को जोड़ते हैं। पेंटियम प्रो की तुलना में, प्राथमिक कैश का आकार दोगुना (16 केबी + 16 केबी) है। प्रोसेसर एक नई हाउसिंग तकनीक का उपयोग करता है - एक प्रिंटेड एज कनेक्टर वाला कार्ट्रिज, जो सिस्टम बस को ले जाता है: S.E.C.C (सिंगल एज कॉन्टैक्ट कार्ट्रिज)। इसे स्लॉट 1 डिज़ाइन में तैयार किया गया था, जिसके लिए स्वाभाविक रूप से पुराने मदरबोर्ड के अपग्रेड की आवश्यकता थी। 14 x 6.2 x 1.6 सेमी मापने वाले कार्ट्रिज में एक प्रोसेसर कोर चिप (सीपीयू कोर), कई चिप्स होते हैं जो सेकेंडरी कैश को लागू करते हैं, और सहायक असतत तत्व (प्रतिरोधक और कैपेसिटर) होते हैं।

इस दृष्टिकोण को एक कदम पीछे माना जा सकता है - इंटेल ने पहले ही दूसरे स्तर के कैश को कोर में एकीकृत करने की तकनीक विकसित कर ली है। लेकिन इस तरह तीसरे पक्ष के निर्माताओं से मेमोरी चिप्स का उपयोग करना संभव था। एक समय में, इंटेल ने इस दृष्टिकोण को अगले 10 वर्षों के लिए आशाजनक माना, हालाँकि थोड़े समय के बाद उसने इसे छोड़ दिया।

साथ ही, सेकेंडरी कैश मेमोरी बस की स्वतंत्रता बनी रहती है, जो अपनी स्थानीय बस द्वारा प्रोसेसर कोर से निकटता से जुड़ी होती है। इस बस की फ्रीक्वेंसी कोर फ्रीक्वेंसी से आधी थी। इसलिए पेंटियम II में आधी प्रोसेसर गति पर चलने वाला एक बड़ा कैश था।

पहला पेंटियम II प्रोसेसर (कोडनाम)। क्लैमथ), जो 7 मई 1997 को सामने आया, इसमें अकेले प्रोसेसर कोर में लगभग 7.5 मिलियन ट्रांजिस्टर शामिल थे और इसे 0.35 माइक्रोन तकनीक का उपयोग करके कार्यान्वित किया गया था। उनके पास 66 मेगाहर्ट्ज की सिस्टम बस आवृत्ति के साथ 233, 266 और 300 मेगाहर्ट्ज की कोर क्लॉक स्पीड थी। उसी समय, द्वितीयक कैश आधी कोर आवृत्ति पर संचालित होता था और उसका वॉल्यूम 512 KB था। इन प्रोसेसरों के लिए, स्लॉट 1 विकसित किया गया था, जिसकी सिग्नल संरचना पेंटियम प्रो के लिए सॉकेट 8 के समान है। हालाँकि, स्लॉट 1 एक सममित मल्टीप्रोसेसर सिस्टम, या निरर्थक कार्यक्षमता नियंत्रण (एफआरसी) वाले सिस्टम को लागू करने के लिए प्रोसेसर की केवल एक जोड़ी को संयोजित करने की अनुमति देता है। तो यह प्रोसेसर एमएमएक्स समर्थन के साथ एक तेज़ पेंटियम प्रो है, लेकिन कम मल्टीप्रोसेसिंग समर्थन के साथ।

26 जनवरी 1998 को, पेंटियम II लाइन का एक प्रोसेसर कोर नाम के साथ जारी किया गया था - उतरता है. से क्लैमथएक पतली तकनीकी प्रक्रिया में भिन्न - 0.25 माइक्रोन और 100 मेगाहर्ट्ज की बस आवृत्ति। इसकी क्लॉक फ्रीक्वेंसी 350, 400, 450 मेगाहर्ट्ज थी। इसे S.E.C.C डिज़ाइन में निर्मित किया गया था, जिसे पुराने मॉडलों में S.E.C.C.2 द्वारा प्रतिस्थापित किया गया था - कोर के एक तरफ एक कैश, और दोनों पर नहीं, जैसा कि मानक डेसच्यूट्स और एक संशोधित कूलर माउंट में होता है। अंतिम कोर आधिकारिक तौर पर पेंटियम II प्रोसेसर में उपयोग किया जाता है, हालांकि नवीनतम पेंटियम II 350-450 मॉडल एक कोर के साथ आए थे जो कटमई की अधिक याद दिलाता था - केवल, निश्चित रूप से, एक छंटनी एसएसई के साथ। एमएमएक्स समर्थन बना हुआ है। प्रथम स्तर का कैश समान 32 KB (16 + 16) है। दूसरे स्तर का कैश भी नहीं बदला है - 512 केबी आधी आवृत्ति पर चल रहा है। प्रोसेसर में 7.5 मिलियन ट्रांजिस्टर शामिल थे और इसे स्लॉट 1 कनेक्टर के लिए तैयार किया गया था।

पेंटियम II ओवरड्राइव- यह पुराने प्रोसेसर पर पेंटियम प्रो को अपग्रेड करने के लिए 11 अगस्त 1998 को जारी किए गए प्रोसेसर का नाम था motherboardsओह, और सॉकेट 8 में काम कर रहा हूं)।

एक कोड नाम था पी6टी. 333 मेगाहर्ट्ज की आवृत्ति थी। पहले स्तर का कैश डेटा के लिए 16 KB + निर्देशों के लिए 16 KB था, दूसरे स्तर के कैश का आकार 512 KB था और इसे कर्नेल में एकीकृत किया गया था। प्रोसेसर फ्रीक्वेंसी पर काम किया। बस 66 मेगाहर्ट्ज। इसमें 7.5 मिलियन ट्रांजिस्टर शामिल थे और इसे 0.25 माइक्रोन प्रक्रिया प्रौद्योगिकी का उपयोग करके उत्पादित किया गया था। एमएमएक्स अनुदेश सेट का समर्थन किया।

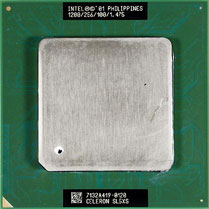

इंटेल के लिए माइक्रोप्रोसेसर प्रौद्योगिकी की दिशा में एक नई शाखा समानांतर मुख्य, "हल्के" और सस्ते विकल्पों की रिहाई थी। ये सीरीज है सेलेरोन. 15 अप्रैल 1998 को पहला प्रोसेसर बुलाया गया सेलेरोनऔर 266 मेगाहर्ट्ज की घड़ी आवृत्ति पर काम कर रहा है।

कोड नाम कोविंगटन. यह प्रोसेसर एक "कट डाउन" पेंटियम II है। सेलेरॉन कोर पर बना है उतरता हैबिना दूसरे स्तर के कैश के। निस्संदेह, इसका असर इसके प्रदर्शन पर पड़ा। लेकिन इसमें बहुत तेजी आई (डेढ़ से दो गुना तक)। अगर पेंटियम ओवरक्लॉकिंग II अधिकतम कैश आवृत्ति द्वारा सीमित था, तब यह वहां था ही नहीं!

सेलेरॉन ने 66 मेगाहर्ट्ज बस पर काम किया और अपने पूर्वज - पेंटियम II डेसच्यूट्स की सभी मुख्य विशेषताओं को दोहराया: प्रथम स्तर कैश - 16 केबी + 16 केबी, एमएमएक्स, 0.25 माइक्रोन प्रक्रिया प्रौद्योगिकी। 7.5 मिलियन ट्रांजिस्टर. प्रोसेसर को एक सुरक्षात्मक कार्ट्रिज - एक डिज़ाइन - S.E.P.P (सिंगल एज पिन पैकेज) के बिना तैयार किया गया था। कनेक्टर - स्लॉट 1.

300 मेगाहर्ट्ज से शुरू होकर, सेलेरॉन प्रोसेसर कोर में एकीकृत 128 केबी एल2 कैश के साथ प्रोसेसर आवृत्ति पर काम करते हुए दिखाई दिए। कोड नाम - Mendocino. 8 अगस्त 1998 को जारी किया गया। फुल-स्पीड कैश के लिए धन्यवाद, इसमें पेंटियम II (समान सिस्टम बस आवृत्ति मानते हुए) की तुलना में उच्च प्रदर्शन है। इन्हें 300 से 533 मेगाहर्ट्ज की घड़ी आवृत्तियों के साथ उत्पादित किया गया था। 30 नवंबर 1998 को, P.P.G.A (प्लास्टिक पिन ग्रिड ऐरे) डिज़ाइन वाला एक प्रोसेसर संस्करण जारी किया गया, जो सॉकेट 370 कनेक्टर में काम करता था।

433 मेगाहर्ट्ज तक इसे दो डिज़ाइनों में तैयार किया गया था: S.E.P.P और P.P.G.A. कुछ समय के लिए, समानांतर में स्लॉट-1 (266 - 433 मेगाहर्ट्ज) और सॉकेट-370 (300ए - 533 मेगाहर्ट्ज) विकल्प थे, अंत में, पहले को धीरे-धीरे बाद वाले से बदल दिया गया।

नया सेलेरॉन पेंटियम की ओर एक कदम था!!!, लेकिन चूंकि यह 66 मेगाहर्ट्ज बस पर चलता था, इसलिए यह एकीकृत हाई-स्पीड कैश के सभी फायदे नहीं दिखा सका। चूंकि कैश को कोर में एकीकृत किया गया था, प्रोसेसर बनाने वाले ट्रांजिस्टर की संख्या में काफी वृद्धि हुई - 19 मिलियन तकनीकी प्रक्रिया वही रही - 0.25 माइक्रोन।

के लिए शक्तिशाली कंप्यूटरइच्छित परिवार जिऑन. पेंटियम II ज़ीऑन पेंटियम II प्रोसेसर का एक सर्वर संस्करण है, जिसने पेंटियम PRO को प्रतिस्थापित किया है। कोर पर निर्मित उतरता हैऔर पेंटियम II से इसकी तेज़ (पूर्ण गति) और अधिक क्षमता (1 या 2 एमबी के साथ विकल्प हैं) दूसरे स्तर के कैश और डिज़ाइन में भिन्न था। इसे स्लॉट 2 के लिए S.E.C.C डिज़ाइन में तैयार किया गया था। यह एक एज कनेक्टर भी है, लेकिन 330 संपर्कों, एक VRM वोल्टेज रेगुलेटर और एक EEPROM स्टोरेज डिवाइस के साथ। मल्टीप्रोसेसर कॉन्फ़िगरेशन में काम करने में सक्षम। इसे 29 जून 1998 को रिलीज़ किया गया था।

पेंटियम प्रो की तरह दूसरे स्तर का कैश फुल-स्पीड है। केवल यहां यह प्रोसेसर के साथ एक ही बोर्ड पर है, और कोर में एकीकृत नहीं है। प्रथम स्तर कैश - 16 केबी + 16 केबी। बस आवृत्ति - 100 मेगाहर्ट्ज। एमएमएक्स अनुदेश सेट का समर्थन किया। प्रोसेसर 400 और 450 मेगाहर्ट्ज की आवृत्तियों पर संचालित होता है। 0.25 माइक्रोन प्रक्रिया प्रौद्योगिकी का उपयोग करके निर्मित। और इसमें 7.5 मिलियन ट्रांजिस्टर थे।

यहीं पर पेंटियम II लाइन का विकास समाप्त होता है। पेंटियम II से शुरू करके, इंटेल ने प्रोसेसर के उत्पादन में तीन मुख्य दिशाओं को अलग किया है: पेंटियम- कार्यस्थानों और घरेलू उपयोग के लिए उच्च-प्रदर्शन प्रोसेसर, सेलेरोन- कार्यालय या घर के लिए पेंटियम का एक बजट संस्करण, जिऑन- बेहतर प्रदर्शन के साथ सर्वर संस्करण।

पेंटियम!!!

पेंटियम नाम वाला पहला प्रोसेसर!!! पेंटियम II से बहुत अलग नहीं। वे 100 मेगाहर्ट्ज की आवृत्ति के साथ एक ही बस पर संचालित होते थे (बाद में, 27 सितंबर, 1999 से, 133 मेगाहर्ट्ज बस पर चलने वाले मॉडल दिखाई दिए), और एस.ई.सी.सी डिजाइन में उत्पादित किए गए थे। 2 और स्लॉट 1 में स्थापना के लिए डिज़ाइन किए गए थे।

कैश मेमोरी वही रहती है: L1 - 16 KB + 16 KB. L2 - 512 KB, प्रोसेसर बोर्ड पर स्थित है, और आधे प्रोसेसर आवृत्ति पर काम कर रहा है। मुख्य अंतर SIMD निर्देशों के सेट का विस्तार है - SSE (स्ट्रीमिंग SIMD एक्सटेंशन)। एमएमएक्स कमांड के सेट का भी विस्तार किया गया है और मेमोरी एक्सेस स्ट्रीमिंग के तंत्र में सुधार किया गया है। कर्नेल कोडनेम कैटमाई. 26 फ़रवरी 1999 को रिलीज़ हुई। प्रोसेसर 450-600 मेगाहर्ट्ज की आवृत्तियों पर संचालित होता था और इसमें 9.5 मिलियन ट्रांजिस्टर होते थे। अपने पूर्ववर्ती की तरह, पेंटियम II डेसच्यूट्स का उत्पादन 0.25 माइक्रोन प्रक्रिया प्रौद्योगिकी का उपयोग करके किया गया था।

तांबे की खान- यह अगले पेंटियम!!! प्रोसेसर कोर का नाम था, जिसने 25 अक्टूबर 1999 को कटमाई का स्थान ले लिया। वास्तव में, कॉपरमाइन एक नया प्रोसेसर है, न कि डेसच्यूट्स का पुनरीक्षण। नए प्रोसेसर में 256 केबी (एडवांस्ड ट्रांसफर कैश) का फुल-स्पीड सेकेंड-लेवल कैश कोर में एकीकृत था।

0.18 माइक्रोन प्रक्रिया प्रौद्योगिकी का उपयोग करके निर्मित। प्रौद्योगिकी को 0.25 से 0.18 माइक्रोन तक पतला करने से इसे कोर पर रखना संभव हो गया बड़ी संख्याट्रांजिस्टर और अब उनमें से 28 मिलियन हैं, जबकि पुराने कटमाई में 9.5 मिलियन थे। सच है, नए पेश किए गए अधिकांश ट्रांजिस्टर एकीकृत L2 कैश से संबंधित हैं। L1 कैश अपरिवर्तित रहा. समर्थित एमएमएक्स और एसएसई कमांड सेट। सबसे पहले S.E.C.C डिज़ाइन में निर्मित किया गया। 2, लेकिन चूंकि कैश अब प्रोसेसर कोर में बनाया गया था, प्रोसेसर बोर्ड अनावश्यक था और केवल प्रोसेसर की लागत में वृद्धि हुई थी। इसलिए, प्रोसेसर जल्द ही एफसी-पीजीए (फ्लिप-चिप पीजीए) डिज़ाइन में आने लगे। सेलेरॉन मेंडोकिनो की तरह, उन्होंने सॉकेट 370 कनेक्टर में काम किया।

सच है, पुराने मदरबोर्ड के साथ सीमित अनुकूलता थी। चूँकि प्रोसेसर अब उच्च क्लॉक स्पीड पर चलता है, कोर शीर्ष पर स्थित था और हीटसिंक के साथ इसका सीधा संपर्क था। कॉपरमाइन स्लॉट 1 के लिए अंतिम प्रोसेसर था। यह 100 और 133 मेगाहर्ट्ज बस पर काम करता था (प्रोसेसर के नाम पर, 133वीं बस को अक्षर द्वारा नामित किया गया था) बी, उदाहरण के लिए - पेंटियम !!! 750बी). कॉपरमाइन कोर वाले प्रोसेसर 533 से 1200 मेगाहर्ट्ज तक की घड़ी की गति पर संचालित होते हैं। 1113 मेगाहर्ट्ज की आवृत्ति के साथ इस कोर पर एक प्रोसेसर जारी करने का पहला प्रयास विफलता में समाप्त हुआ, क्योंकि यह चरम मोड में बहुत अस्थिर था, और इस आवृत्ति वाले सभी प्रोसेसर को वापस बुला लिया गया था - इस घटना ने इंटेल की प्रतिष्ठा को बहुत खराब कर दिया।

मुख्य टुआलाटिन 21 जून 2001 को कॉपरमाइन का स्थान ले लिया गया। इस समय, पहले पेंटियम 4 प्रोसेसर पहले से ही बाज़ार में थे, और नए प्रोसेसर का उद्देश्य नए 0.13 माइक्रोन का परीक्षण करना था। प्रौद्योगिकी, और उच्च-प्रदर्शन प्रोसेसर के स्थान को भरने के लिए भी, क्योंकि पहले पेंटियम 4 का प्रदर्शन काफी कम था। ट्यूलैटिन प्रोसेसर उत्पादन को 0.13-माइक्रोन प्रौद्योगिकी में परिवर्तित करने की इंटेल की वैश्विक परियोजना का मूल नाम है। नए कोर वाले प्रोसेसर स्वयं इस परियोजना के हिस्से के रूप में सामने आने वाले पहले उत्पाद थे।

कर्नेल में कुछ बदलाव हैं - केवल "डेटा प्रीफ़ेच लॉजिक" तकनीक जोड़ी गई है। यह एप्लिकेशन के लिए आवश्यक डेटा को कैश में प्रीलोड करके प्रदर्शन में सुधार करता है। इसके अलावा, इन कोर के बीच का अंतर उपयोग की जाने वाली उत्पादन तकनीक में निहित है - कॉपरमाइन का निर्माण 0.18 माइक्रोन तकनीक का उपयोग करके किया जाता है, और ट्यूलैटिन का निर्माण 0.13 माइक्रोन तकनीक का उपयोग करके किया जाता है। नए प्रोसेसर के लिए सॉकेट वही रहता है - सॉकेट 370, लेकिन डिज़ाइन एफसी-पीजीए 2 में बदल गया है, जिसका उपयोग पेंटियम 4 प्रोसेसर में किया गया था। यह पुराने एफसी-पीजीए से मुख्य रूप से अलग है क्योंकि कोर गर्मी से ढका हुआ है -डिसिपेटिंग प्लेट, जो रेडिएटर स्थापित करते समय इसे क्षति से भी बचाती है।

हैप्पी ट्यूलैटिन, पेंटियम लाइन!!! दो वर्गों में "विभाजित" - डेस्कटॉप और सर्वर प्रोसेसर। पूर्व के लिए, L2 कैश वॉल्यूम 256 KB के बराबर रहा, बाद वाले के लिए यह दोगुना होकर 512 KB हो गया; इसके अलावा, नए P-III (तथाकथित डेस्कटॉप ट्यूलैटिन) के डेस्कटॉप संस्करण में SMP समर्थन का अभाव था। प्रथम स्तर कैश - 16 केबी + 16 केबी। यह कहा जाना चाहिए कि डेस्कटॉप ट्यूलैटिन लंबे समय तक नहीं चला: इसकी आपूर्ति केवल बड़े पीसी असेंबलरों को की गई थी, और पेंटियम 4 के साथ प्रतिस्पर्धा न करने के लिए इसे बाजार से वापस ले लिया गया था। लेकिन पेंटियम !!!-एस, का सर्वर संस्करण प्रोसेसर, शक्तिशाली सर्वर प्रोसेसर के स्थान पर कब्जा करने वाला था, क्योंकि ज़ीऑन प्रोसेसर का प्रदर्शन अब पर्याप्त नहीं था, और पेंटियम 4 में एसएमपी समर्थन नहीं था, और आम तौर पर कम प्रदर्शन दिखाया गया था।

जैसा कि ऊपर उल्लेख किया गया है, टुआलाटिन प्रोसेसर अधिक उन्नत 0.13 माइक्रोन का उपयोग करके उत्पादित किए गए थे। तकनीकी प्रक्रिया, 133 मेगाहर्ट्ज की आवृत्ति के साथ एक बस पर संचालित होती है और इसमें 44 मिलियन ट्रांजिस्टर शामिल होते हैं। समर्थित एमएमएक्स और एसएसई निर्देश सेट। प्रोसेसर 1 गीगाहर्ट्ज से 1.33 गीगाहर्ट्ज (डेस्कटॉप ट्यूलैटिन) और 1.13 गीगाहर्ट्ज से 1.4 गीगाहर्ट्ज (सर्वर संस्करण) की आवृत्तियों पर संचालित होता है।

अभी हाल ही में मुझे कुछ बहुत ही रोचक जानकारी मिली - यह पता चला कि इंटेल एक प्रोसेसर विकसित कर रहा था जिसे पेंटियम लाइन की निरंतरता माना जाता था !!! यह प्रोसेसर 0.13 माइक्रोन का उपयोग करके उन्नत ट्यूलैटिन कोर पर आधारित था। तकनीकी प्रक्रिया. सामान्य ट्यूलैटिन से इसका मुख्य अंतर इसका बढ़ा हुआ आकार 1024 केबी था। एल2 कैश और 166 मेगाहर्ट्ज सिस्टम बस! आवृत्तियों को कम से कम 2.0 गीगाहर्ट्ज तक पहुंचना होगा। लेकिन इंटेल, पेंटियम 4 प्रोसेसर पर भरोसा करते हुए, नए ट्यूलैटिन को मना कर देता है। आखिरकार, भले ही सेलेरॉन ट्यूलैटिन, लगभग 1.7 गीगाहर्ट्ज़ की आवृत्तियों पर ओवरक्लॉक किया गया, आसानी से न केवल सेलेरॉन विलमेट के साथ प्रतिस्पर्धा करता है, बल्कि पेंटियम 4 के साथ भी प्रतिस्पर्धा करता है, फिर भी एक विशाल कैश और तेज़ बस से लैस नया ट्यूलैटिन नहीं होगा उन्हें कोई भी मौका छोड़ें.

पेंटियम!!! प्रोसेसर जारी होने के बाद, इंटेल ने बजट प्रोसेसर बाजार में अपनी स्थिति न खोने के लिए, सेलेरॉन लाइन जारी करना जारी रखा। अब ये पूरी तरह से अलग प्रोसेसर थे - इंटेल ने सेलेरॉन नामक पहला प्रोसेसर बनाने का अनुभव दोहराया: यह पेंटियम प्रोसेसर कोर का उपयोग करता है!!! दूसरे स्तर के कैश को घटाकर 128 केबी और धीमी 66 मेगाहर्ट्ज बस के साथ।

29 मार्च, 2000 पहला सेलेरॉन कोर प्रोसेसर सामने आया तांबे की खान 128या कॉपरमाइन लाइट.

जैसा कि नाम से पता चलता है, प्रोसेसर आधे दूसरे स्तर के कैश के साथ कॉपरमाइन कोर पर आधारित है। बिल्कुल अपने बड़े भाई की तरह - पेंटियम!!! कॉपरमाइन, नया सेलेरॉन, अतिरिक्त एसएसई निर्देशों का एक सेट, तेज़ अंतर्निहित कैश मेमोरी है और इसे एक ही तकनीकी मानक (0.18 माइक्रोन) के अनुसार निर्मित किया गया है, जो केवल दूसरे स्तर के कैश के आकार में भिन्न है - 128 केबी बनाम 256 केबी पेंटियम के लिए!!! (सबसे आपत्तिजनक बात यह है कि कैश भौतिक रूप से प्रोसेसर में मौजूद है, यह बस अक्षम है)। उसी सॉकेट 370 कनेक्टर में काम करता है।

पहला प्रोसेसर 566 मेगाहर्ट्ज की आवृत्ति के साथ दिखाई दिया और 66 मेगाहर्ट्ज बस पर चला। बाद में, 3 जनवरी 2001 को, 800 मेगाहर्ट्ज संस्करण की रिलीज़ के साथ, सेलेरॉन तेज़ 100 मेगाहर्ट्ज बस में बदल गया। इन प्रोसेसर की अधिकतम आवृत्ति 1100 मेगाहर्ट्ज थी। स्तर 1 कैश: 32 केबी (डेटा के लिए 16 केबी और निर्देशों के लिए 16 केबी)। प्रोसेसर में 28.1 मिलियन ट्रांजिस्टर शामिल थे।

सेलेरॉन पहले कभी पेंटियम प्रोसेसर के इतना करीब नहीं था। पेंटियम से!!! डेस्कटॉप ट्यूलैटिन केवल धीमी 100 मेगाहर्ट्ज बस में भिन्न था। सामान्य तौर पर, दूसरे स्तर के कैश के आकार को अपरिवर्तित छोड़कर और डेस्कटॉप उपयोग के लिए ट्यूलैटिन कोर के लिए एफएसबी आवृत्ति को 100 मेगाहर्ट्ज तक कम करके, इंटेल ने "नया सेलेरॉन" जारी किया। प्रोसेसर 900 मेगाहर्ट्ज से 1400 मेगाहर्ट्ज तक की घड़ी आवृत्तियों के साथ उत्पादित किए गए थे, जिसमें 44 मिलियन ट्रांजिस्टर शामिल थे, जो एमएमएक्स, एसएसई समर्थित थे। तकनीकी प्रक्रिया 0.13 माइक्रोन। इन्हें सॉकेट 370 कनेक्टर के लिए FC-PGA 2 डिज़ाइन में तैयार किया गया था।

हैप्पी पेंटियम रिलीज़!!! इंटेल का उत्पादन जारी है सर्वर प्रोसेसरनई पीढ़ी के पेंटियम पर आधारित। 17 मार्च 1999 को पेंटियम श्रृंखला का पहला प्रोसेसर जारी किया गया!!! ज़ीऑन।

कर्नेल कोडनेम चर्मकार. पेंटियम बेस पर बनाया गया था!!! कटमई. 512, 1024 या 2048 केबी फुल-स्पीड द्वितीय-स्तरीय मेमोरी कैश शामिल है। प्रथम स्तर कैश - 16 केबी + 16 केबी। इसे 0.25 माइक्रोन का उपयोग करके 500 और 550 मेगाहर्ट्ज की आवृत्तियों के साथ उत्पादित किया गया था। तकनीकी प्रक्रिया, और इसमें 9.5 मिलियन ट्रांजिस्टर शामिल थे। 100 मेगाहर्ट्ज सिस्टम बस पर संचालित। इसे स्लॉट 2 के लिए S.E.C.C डिज़ाइन में तैयार किया गया था। इसका उद्देश्य दो-, चार-, आठ-प्रोसेसर (या अधिक) सर्वर और वर्कस्टेशन में उपयोग करना था।

पेंटियम में सुखद परिवर्तन!!! नए कोर पर, 25 अक्टूबर 1999 को, नए कोर के साथ ज़ीऑन प्रोसेसर का एक संशोधन दिखाई दिया झरने. यह मूलतः एक उन्नत कॉपरमाइन कोर था। प्रोसेसर में 256 केबी से 2048 केबी तक दूसरे स्तर का मेमोरी कैश था, जो 100 और 133 मेगाहर्ट्ज (संस्करण के आधार पर) की सिस्टम बस आवृत्तियों पर संचालित होता था। प्रोसेसर 600 से 900 मेगाहर्ट्ज की आवृत्तियों के साथ उत्पादित किए गए थे। पहले बैच के 900 मेगाहर्ट्ज की आवृत्ति वाले प्रोसेसर अत्यधिक गर्म हो गए और उनकी डिलीवरी अस्थायी रूप से निलंबित कर दी गई। अपने पूर्ववर्ती की तरह, Xeon Cascades को स्लॉट 2 कनेक्टर में इंस्टॉलेशन के लिए डिज़ाइन किया गया था, इसे 0.18 माइक्रोन का उपयोग करके तैयार किया गया था। तकनीकी प्रक्रिया और इसमें 28.1 मिलियन ट्रांजिस्टर शामिल थे। दो-, चार- और आठ-प्रोसेसर सर्वर और वर्कस्टेशन में काम कर सकता है।

कर्नेल आधारित टुआलाटिनज़ीऑन प्रोसेसर जारी नहीं किए गए थे। उनका स्थान पेंटियम!!!-एस ने ले लिया, जिसका वर्णन मैंने ऊपर किया है। ज़ीऑन प्रोसेसरसमर्थित एमएमएक्स और एसएसई कमांड सेट।

पेंटियम 4

पेंटियम प्रोसेसर की आवृत्ति बढ़ाने का प्रयास करते समय बहुत सारी समस्याओं का सामना करना पड़ा!!! 1 गीगाहर्ट्ज से ऊपर के कॉपरमाइन कोर पर, इंटेल इंजीनियरों ने महसूस किया कि पुराने प्रोसेसर आर्किटेक्चर, पेंटियम प्रो के बाद से अपरिवर्तित, में आमूल-चूल परिवर्तन की आवश्यकता है। और यद्यपि 0.13 माइक्रोन उत्पादन में परिवर्तन से पेंटियम को मदद मिलेगी!!! इसे अपना काम अच्छी तरह से करने में लगभग एक साल लगेगा, इस आर्किटेक्चर की क्षमता लगभग समाप्त हो चुकी है और कंपनी ने अपने नए 32-बिट प्रोसेसर के लिए एक नया आर्किटेक्चर विकसित किया है, जिसे वह इंटेल नेटबर्स्ट माइक्रो-आर्किटेक्चर कहता है। प्रोसेसर को कई गीगाहर्ट्ज़ की आवृत्तियों पर संचालित करने के लिए, इंटेल ने पेंटियम 4 पाइपलाइन की लंबाई को 20 चरणों (हाइपर पाइपलाइन टेक्नोलॉजी) तक बढ़ा दिया है, जिसके कारण तकनीकी मानकों के साथ भी 2 गीगाहर्ट्ज़ की आवृत्ति पर प्रोसेसर संचालन प्राप्त करना संभव हो सका। 0.18 माइक्रोन का. हालाँकि, पाइपलाइन की लंबाई में इस वृद्धि के कारण, प्रोसेसर चक्रों में एक निर्देश का निष्पादन समय भी काफी बढ़ जाता है। इसलिए, कंपनी ने ट्रांज़िशन प्रेडिक्शन एल्गोरिदम (एडवांस्ड डायनेमिक एक्ज़ीक्यूशन) पर कड़ी मेहनत की है।

प्रोसेसर में लेवल 1 कैश में महत्वपूर्ण बदलाव हुए हैं। पेंटियम!!! के विपरीत, जिसका कैश निर्देश और डेटा संग्रहीत कर सकता है, पेंटियम 4 में केवल 8 KB डेटा कैश है। कमांड तथाकथित ट्रेस कैश में सहेजे जाते हैं। वहां वे पहले से ही डिकोडेड फॉर्म में संग्रहीत हैं, यानी। प्रोसेसर के एक्चुएटर्स में निष्पादन के लिए प्राप्त सूक्ष्म संचालन के अनुक्रम के रूप में। इस कैश की क्षमता 12,000 माइक्रो-ऑप्स है।

साथ ही नए प्रोसेसर में कमांड के सेट का विस्तार किया गया - एसएसई2. 70 एसएसई निर्देशों में, अन्य 144 नए निर्देश जोड़े गए। कई नवाचारों में से एक पूरी तरह से नई 100 मेगाहर्ट्ज बस थी, जो प्रति घड़ी 4 डेटा पैकेट संचारित करती थी - क्यूपीबी (क्यूउड पीअवस्र्द्ध बीहमें), जिसके परिणामस्वरूप 400 मेगाहर्ट्ज की आवृत्ति मिलती है।

पेंटियम 4 श्रृंखला का पहला कोर वाला प्रोसेसर था विलमेट 423.

20 नवंबर 2000 को 1.4 और 1.5 गीगाहर्ट्ज की आवृत्तियों के साथ प्रदर्शित होने वाले, 0.18 माइक्रोन प्रक्रिया प्रौद्योगिकी का उपयोग करके निर्मित ये प्रोसेसर 2 गीगाहर्ट्ज की आवृत्ति तक पहुंच गए। प्रोसेसर को नए सॉकेट 423 में स्थापित किया गया था और इसे FC-PGA 2 डिज़ाइन में तैयार किया गया था, इसमें 42 मिलियन ट्रांजिस्टर शामिल थे।

दूसरे स्तर के कैश का आकार समान रहा - 256 KB। L2 कैश बस की चौड़ाई 256 बिट है, लेकिन कैश विलंबता को आधा कर दिया गया है, जिससे 1.5 गीगाहर्ट्ज़ पर 48 जीबी कैश बैंडविड्थ की अनुमति मिलती है।

चूंकि नए प्रोसेसर का आर्किटेक्चर मुख्य रूप से आवृत्ति बढ़ाने पर केंद्रित था, इसलिए यह आश्चर्य की बात नहीं है कि पहले पेंटियम 4 प्रोसेसर बेहद कम प्रदर्शन दिखाते हैं। अधिकांश कार्यों में 1.4 गीगाहर्ट्ज़ प्रोसेसर पेंटियम से कमतर था!!! कॉपरमाइन, 1000 मेगाहर्ट्ज पर काम कर रहा है।

बाद में, 27 अगस्त 2001 को, कोर वाले प्रोसेसर विल्मेटनए कनेक्टर में स्थापना के लिए इरादा - सॉकेट 478। प्रोसेसर ने डिज़ाइन - एमपीजीए और सॉकेट 478 कनेक्टर के अपवाद के साथ, अपने पूर्वज की सभी विशेषताओं को दोहराया।

पिछला सॉकेट 423 फॉर्म फैक्टर "संक्रमणकालीन" था और इंटेल भविष्य में इसका समर्थन नहीं करेगा। प्रोसेसर का आकार इस तथ्य के कारण कम हो गया है कि पिन अब सीधे प्रोसेसर कोर के नीचे बनाए जाते हैं। यह प्रोसेसर, अपने पूर्ववर्ती की तरह, 1.4 से 2.0 गीगाहर्ट्ज़ की आवृत्तियों पर संचालित होता है।

नॉर्थवुड- यह अगले कोर का नाम है, जिस पर आज भी पेंटियम 4 प्रोसेसर का उत्पादन किया जाता है।

0.13 µm पर जाएँ. तकनीकी प्रक्रिया ने घड़ी की आवृत्ति को और बढ़ाना और दूसरे स्तर के कैश को 512 केबी तक बढ़ाना संभव बना दिया। प्रोसेसर बनाने वाले ट्रांजिस्टर की संख्या में भी वृद्धि हुई है - अब उनमें से 55 मिलियन हैं, स्वाभाविक रूप से, एमएमएक्स, एसएसई और एसएसई2 निर्देश सेट के लिए समर्थन बना हुआ है।

नॉर्थवुड कोर पर आधारित पहला प्रोसेसर 7 अगस्त 2001 को 2.0 गीगाहर्ट्ज की आवृत्ति और 400 मेगाहर्ट्ज (4 * 100 मेगाहर्ट्ज) की सिस्टम बस आवृत्ति के साथ दिखाई दिया। आज, नॉर्थवुड प्रोसेसर 1.6 से 3.2 गीगाहर्ट्ज़ की आवृत्ति पर काम करते हैं। समान आवृत्तियों पर, लेकिन विभिन्न कोर के साथ काम करने वाले प्रोसेसर के साथ भ्रम से बचने के लिए, इंटेल फिर से अक्षर चिह्नों का उपयोग करता है। उदाहरण के लिए, पेंटियम 1.8 ए, जहां पत्र एएक नए कोर और बड़े L2 कैश को इंगित करता है।

6 मई 2002 को, इंटेल ने 533 मेगाहर्ट्ज (4 * 133 मेगाहर्ट्ज) की सिस्टम बस आवृत्ति और 2.26 गीगाहर्ट्ज की क्लॉक स्पीड के साथ नॉर्थवुड कोर पर आधारित एक प्रोसेसर जारी किया। चूंकि 400 मेगाहर्ट्ज की बस आवृत्ति वाले मॉडल 2.6 गीगाहर्ट्ज तक की आवृत्तियों के साथ तैयार किए गए थे, इसलिए यहां भी अक्षर चिह्नों का उपयोग किया गया था। बिल्कुल पेंटियम प्रोसेसर की तरह!!! पत्र द्वारा 133 मेगाहर्ट्ज बस की उपस्थिति का संकेत दिया गया था बी. उदाहरण के लिए, पेंटियम 4 2.4 बी.

लेकिन इंटेल यहीं नहीं रुकता, और 14 अप्रैल, 2003 को, उसने उसी नॉर्थवुड कोर पर आधारित एक प्रोसेसर जारी किया, लेकिन 800 मेगाहर्ट्ज (4 * 200 मेगाहर्ट्ज) की सिस्टम बस आवृत्ति और 3.0 गीगाहर्ट्ज की घड़ी आवृत्ति के साथ। बाद में, 800 मेगाहर्ट्ज सिस्टम बस वाले प्रोसेसर का उत्पादन 2.4 गीगाहर्ट्ज से कम आवृत्तियों के साथ किया जाने लगा। नई बस को इंगित करने के लिए, प्रोसेसर मार्किंग में एक अक्षर दिखाई देता है सी. उदाहरण के लिए, पेंटियम 4 2.4 सी. (इस प्रकार, अलग-अलग बस आवृत्तियों के साथ 2.4 गीगाहर्ट्ज प्रोसेसर के तीन संशोधन हैं, जो 2 के कारक से भिन्न हैं!)

सभी 800 मेगाहर्ट्ज एफएसबी प्रोसेसर नई तकनीक का समर्थन करते हैं हिंदुस्तान टाइम्स, जिसका अर्थ है हाइपर थ्रेडिंग.

पेंटियम 4HT

14 नवंबर 2002 को, पेंटियम 4 प्रोसेसर को 3.06 गीगाहर्ट्ज की आवृत्ति और 533 मेगाहर्ट्ज की सिस्टम बस आवृत्ति के समर्थन के साथ जारी किया गया था। नई टेक्नोलॉजी हाइपर थ्रेडिंग.

हाइपर-थ्रेडिंग वाले एक भौतिक प्रोसेसर को सिस्टम द्वारा दो के रूप में देखा जाता है, जो आपको इसके संसाधनों के लोड को अनुकूलित करने और प्रदर्शन में सुधार करने की अनुमति देता है। हाइपर-थ्रेडिंग का संचालन सिद्धांत इस तथ्य पर आधारित है कि किसी भी समय निष्पादन करते समय प्रोसेसर संसाधनों का केवल एक हिस्सा ही उपयोग किया जाता है। प्रोग्राम कोड. अप्रयुक्त संसाधनों को भी काम के साथ लोड किया जा सकता है - उदाहरण के लिए, समानांतर निष्पादन के लिए किसी अन्य एप्लिकेशन (या उसी एप्लिकेशन का कोई अन्य थ्रेड) का उपयोग किया जा सकता है।

HT वास्तविक मल्टीप्रोसेसिंग नहीं है, क्योंकि सीधे कमांड निष्पादित करने वाले ब्लॉक की संख्या नहीं बदली है। केवल उनके उपयोग की दक्षता में वृद्धि हुई है। इसलिए, किसी विशिष्ट प्रोग्राम को HT के लिए जितना बेहतर अनुकूलित किया जाएगा, प्रदर्शन लाभ उतना ही अधिक होगा। इंटेल के अनुसार, एचटी से लाभ 30% तक पहुंच सकता है, जबकि इसे लागू करने वाले ब्लॉक पेंटियम 4 के कुल क्षेत्र के 5% से कम पर कब्जा करते हैं, हालांकि, यहां तक कि पूरी तरह से अनुकूलित एप्लिकेशन भी, उदाहरण के लिए, डेटा तक पहुंच सकते हैं कैश-प्रोसेसर मेमोरी में नहीं है, जिसके कारण यह निष्क्रिय है। यदि नेटबर्स्ट आर्किटेक्चर को मेगाहर्ट्ज़ की संख्या बढ़ाने के लिए डिज़ाइन किया गया था, तो इसके विपरीत, हाइपर-थ्रेडिंग को प्रति घड़ी चक्र में किए गए कार्य को बढ़ाने के लिए डिज़ाइन किया गया है।

पेंटियम 4 में हाइपर-थ्रेडिंग की देर से शुरूआत के कारणों में से एक (समर्थन न केवल नॉर्थवुड कोर में मौजूद है, बल्कि विलमेट में भी मौजूद है, लेकिन अवरुद्ध था) विंडोज एक्सपी का अपेक्षाकृत कम प्रचलन था - एकमात्र ओएस विंडोज़ परिवार जो नई तकनीक का पूर्ण समर्थन करता है। प्रौद्योगिकी को मदरबोर्ड के चिपसेट और BIOS द्वारा भी समर्थित होना चाहिए।

आज, हाइपर-थ्रेडिंग तकनीक 533 मेगाहर्ट्ज की सिस्टम बस आवृत्ति वाले पेंटियम 4 3.06 गीगाहर्ट्ज प्रोसेसर के साथ-साथ 800 मेगाहर्ट्ज की बस आवृत्ति वाले सभी प्रोसेसर द्वारा समर्थित है।

सॉकेट 478 के लिए पेंटियम 4 विलमेट की रिलीज़ के बाद, सॉकेट 370 के लिए प्रोसेसर को बाज़ार से बाहर करने के लिए, और साथ ही, बजट प्रोसेसर (जहां सेलेरॉन ट्यूलैटिन पहले था) के स्थान पर कब्ज़ा करना चाहते हैं, इंटेल ने सेलेरॉन को इसके आधार पर रिलीज़ किया। मुख्य विलमेट 128.

विलमेट 128 कोर वास्तुशिल्प रूप से पेंटियम 4 विलमेट कोर से अलग नहीं है। कैश का संगठन और इसके ऑपरेटिंग एल्गोरिदम नहीं बदले हैं, केवल आकार में अंतर है - मूल पेंटियम 4 विलमेट में 256 केबी के बजाय दूसरे स्तर के कैश का 128 केबी।

स्वाभाविक रूप से, सॉकेट 478 फॉर्म फैक्टर को भी बरकरार रखा गया है, जिसे इंटेल लंबे समय तक उपयोग करने की योजना बना रहा है। इस प्रकार, इंटेल अपने प्रोसेसर को एक प्लेटफ़ॉर्म पर स्थानांतरित कर रहा है, ताकि बाद के अपग्रेड के दौरान आपको प्रोसेसर के साथ-साथ मदरबोर्ड को बदलने की आवश्यकता न पड़े।

15 मई 2002 को, सेलेरॉन नामक पहला प्रोसेसर सामने आया, जो 1.7 गीगाहर्ट्ज़ की आवृत्ति के साथ पेंटियम 4 पर बनाया गया था। बाद में, 12 जून 2002 को 1.8 गीगाहर्ट्ज़ संस्करण सामने आया।

नया सेलेरॉन, पहले की तरह, 100 मेगाहर्ट्ज सिस्टम बस का उपयोग करता है, हालांकि अब प्रति घड़ी 4 सिग्नल के प्रसारण के साथ। चौगुनी 100 मेगाहर्ट्ज एफएसबी आखिरकार एफएसबी बैंडविड्थ की कमी की पुरानी सेलेरॉन समस्या को हल कर देती है।

पेंटियम 4 विलमेट की तरह, नया सेलेरॉन 0.18 माइक्रोन का उपयोग करके बनाया गया है। तकनीकी प्रक्रिया. 42 मिलियन ट्रांजिस्टर से मिलकर बनता है। 1.7 और 1.8 GHz की आवृत्तियों के साथ उपलब्ध है।

सेलेरॉन प्रोसेसर का आज का अगला और आखिरी कोर है नॉर्थवुड(स्वाभाविक रूप से दूसरे स्तर के कैश को घटाकर 128 केबी कर दिया गया है)। इस कोर पर आधारित पहला प्रोसेसर सेलेरॉन 2.0 गीगाहर्ट्ज़ था, जो 18 सितंबर 2002 को जारी किया गया था। यह, सेलेरॉन विलमेट 128 की तरह, अपने बड़े भाई पेंटियम 4 नॉर्थवुड की विशेषताओं को पूरी तरह से दोहराता है, विशेष रूप से 400 मेगाहर्ट्ज (4 * 100 मेगाहर्ट्ज) के लिए डिज़ाइन की गई बस और 128 केबी आकार के दूसरे स्तर के कैश को छोड़कर।

अनुप्रयोग 0.13 माइक्रोन. तकनीकी प्रक्रिया अच्छी ओवरक्लॉकेबिलिटी का लाभ देती है। नॉर्थवुड कोर में अच्छी आवृत्ति क्षमता है (वर्तमान में 3.2 गीगाहर्ट्ज तक), इसलिए ओवरक्लॉकिंग के लिए जगह है।

Intel Pentium II Xeon की पहली रिलीज़ को तीन साल से थोड़ा कम समय बीत चुका है। और इंटेल ने 21 मई 2001 को, अपने प्रोसेसरों को विभाजित करने के अपने क्रम को जारी रखते हुए, अगली पीढ़ी के ज़ीऑन प्रोसेसर की घोषणा की, जो पर आधारित है पेंटियम कोर 4 विलमेट. प्रोसेसर को पुराने तरीके से Intel Xeon कहा जाता है, और यह तीन वेरिएंट में उपलब्ध है: 1.4 GHz, 1.5 GHz और 1.7 GHz। मामूली विवरणों को छोड़कर, प्रोसेसर कोर लगभग पूरी तरह से पेंटियम 4 के नियमित (डेस्कटॉप) संस्करण के समान है। इसका मतलब यह है कि नए ज़ीऑन में वह सब कुछ है जो पेंटियम 4 में है - नए आर्किटेक्चर के फायदे और नुकसान दोनों।

पहले ज़ीऑन मॉडल 0.18 माइक्रोन का उपयोग करके तैयार किए गए थे। तकनीकी प्रक्रिया, एक कोर के साथ जो लगभग पेंटियम 4 विलमेट के समान था और कोड नाम रखता था पोषक. प्रोसेसर को 2.0 गीगाहर्ट्ज तक की क्लॉक स्पीड के साथ तैयार किया गया था। 42 मिलियन ट्रांजिस्टर से मिलकर बना।

लेवल 1 कैश मेमोरी, पेंटियम 4 लाइन के सभी प्रोसेसर की तरह, नेटबर्स्ट आर्किटेक्चर के साथ, 8 केबी डेटा कैश। दूसरे स्तर का कैश - बेहतर डेटा ट्रांसफर के साथ 256 केबी (256 केबी एडवांस्ड ट्रांसफर कैश)। पेंटियम 4 विलमेट की तरह, नया ज़ीऑन 400 मेगाहर्ट्ज सिस्टम बस (4 * 100 मेगाहर्ट्ज) का उपयोग करता है जो 400 मेगाहर्ट्ज की आवृत्ति पर दो मेमोरी चैनलों को समकालिक रूप से संचालित करता है।

ऐतिहासिक रूप से, इंटेल ज़ीऑन प्रोसेसर लाइनें (यानी पेंटियम II ज़ीऑन, पेंटियम III ज़ीऑन) ने हमेशा एक अलग का उपयोग किया है नियमित संस्करणप्रोसेसर डिज़ाइन जबकि पेंटियम II और पेंटियम III प्रोसेसर 242-पिन स्लॉट1 संस्करण में निर्मित किए गए थे, उनके ज़ीऑन संस्करणों में 330-पिन स्लॉट-2 कनेक्टर का उपयोग किया गया था। अधिकांश अतिरिक्त पैरों का उपयोग चिप को अतिरिक्त बिजली की आपूर्ति करने के लिए किया गया था। दो मेगाबाइट L2 कैश के साथ, पेंटियम III Xeon ने अपने 256 KB समकक्ष की तुलना में अधिक बिजली की खपत की। नई Xeon के साथ भी ऐसी ही स्थिति उत्पन्न हुई। जबकि पहले पेंटियम 4 विलमेट प्रोसेसर में 423-पिन सॉकेट का उपयोग किया जाता था, ज़ीऑन सॉकेट 603 में उपयोग के लिए डिज़ाइन किए गए 603-पिन इंटरफ़ेस का उपयोग करता है। प्रोसेसर केवल सिंगल- या डुअल-प्रोसेसर कॉन्फ़िगरेशन में काम कर सकता है।

9 जनवरी 2002 को, 0.13 माइक्रोन का उपयोग करते हुए नॉर्थवुड कोर पर आधारित ज़ीऑन प्रोसेसर सामने आया। तकनीकी प्रक्रिया, और 512 केबी द्वितीय स्तर कैश से सुसज्जित। कर्नेल कोड नाम - प्रेस्टोनिया. यह अपने पूर्ववर्ती, ज़ीऑन फोस्टर से केवल अपने बड़े कैश और अधिक उन्नत तकनीकी प्रक्रिया में भिन्न है। प्रोसेसर 1.8 गीगाहर्ट्ज़ से 3.0 गीगाहर्ट्ज़ तक की आवृत्तियों पर काम करते हैं। 55 मिलियन ट्रांजिस्टर से मिलकर बनता है। प्रेस्टोनिया कोर वाले प्रोसेसर अब पहली बार हाइपर-थ्रेडिंग का समर्थन करते हैं।

12 मार्च 2002 को ज़ीऑन एमपी प्रोसेसर जारी किया गया। 0.18 माइक्रोन का उपयोग करके निर्मित। और 256 KB L2 कैश से सुसज्जित है। ज़ीऑन फोस्टर प्रोसेसर से मुख्य अंतर मल्टीप्रोसेसर सिस्टम में काम करने की क्षमता है। वे 1.4 से 1.6 गीगाहर्ट्ज़ तक की आवृत्तियों पर काम करते हैं। ये प्रोसेसर हाइपर-थ्रेडिंग तकनीक को भी सपोर्ट करते हैं।

4 नवंबर 2002 को, 0.13 माइक्रोन का उपयोग करके निर्मित Xeon MP प्रोसेसर सामने आए। तकनीकी प्रक्रिया. 1.5 गीगाहर्ट्ज, 1.9 गीगाहर्ट्ज और 2.0 गीगाहर्ट्ज की आवृत्तियों पर काम करने वाले ये प्रोसेसर, अपने साथी ज़ीऑन प्रेस्टोनिया से न केवल मल्टीप्रोसेसर कॉन्फ़िगरेशन में काम करने की क्षमता में भिन्न हैं, बल्कि 1 या 2 एमबी के एकीकृत तीसरे स्तर के कैश की उपस्थिति में भी भिन्न हैं। आकार में। इसके कारण, प्रोसेसर बनाने वाले ट्रांजिस्टर की संख्या बढ़कर 108 मिलियन हो गई है!

18 नवंबर 2002 को, 533 मेगाहर्ट्ज (4 * 133 मेगाहर्ट्ज) सिस्टम बस पर चलने वाले ज़ीऑन प्रोसेसर दिखाई दिए। ये प्रोसेसर 0.13 माइक्रोन का उपयोग करके प्रेस्टोनिया कोर पर बनाए गए हैं। तकनीकी प्रक्रिया और इसमें 108 मिलियन ट्रांजिस्टर शामिल हैं। द्वितीय स्तर की कैश मेमोरी - 512 KB। तृतीय स्तर कैश 1 एमबी। 533 मेगाहर्ट्ज बस पर ज़ीऑन प्रोसेसर 2.0 गीगाहर्ट्ज़ से 3.06 गीगाहर्ट्ज़ (10 मार्च 2003 को जारी) की घड़ी आवृत्तियों के साथ उपलब्ध हैं। हाल ही में 3.2 गीगाहर्ट्ज़ प्रोसेसर की भी घोषणा की गई थी।

2003 के अंत में, इंटेल अपने प्रोसेसर के लिए एक नया कोर पेश करेगा - प्रेस्कॉट. इन प्रोसेसर का निर्माण 0.09 माइक्रोन का उपयोग करके किया जाएगा। (90 एनएम) प्रौद्योगिकी। प्रेस्कॉट कोर में 125 मिलियन ट्रांजिस्टर होंगे और इसमें 1 एमबी द्वितीय-स्तरीय कैश होगा। साथ ही, यह भी संभव है कि प्रथम स्तर का कैश अंततः 32 KB तक बढ़ा दिया जाएगा। स्वाभाविक रूप से, नया कोर हाइपर-थ्रेडिंग तकनीक का समर्थन करेगा। बस ये तो पहले से ही होगा हाइपर-थ्रेडिंग 2, इससे आगे का विकासएक चिप में "मल्टीप्रोसेसिंग"। उनके अंतर क्या होंगे यह अभी तक ज्ञात नहीं है, लेकिन ऐसी धारणाएं हैं (किसी ने पुष्टि नहीं की है) कि नया उत्पाद आपको एक भौतिक प्रोसेसर में दो नहीं, बल्कि कई वर्चुअल प्रोसेसर देखने की अनुमति देता है।

एक नया निर्देश सेट भी जोड़ा जाएगा (या मौजूदा एक विस्तारित), जिसमें फ़्लोटिंग पॉइंट संख्याओं को पूर्णांकों में परिवर्तित करने के लिए 15 नए निर्देश, जटिल संख्या अंकगणित, वीडियो डिकोडिंग के लिए विशेष निर्देश, फ़्लोटिंग पॉइंट प्रारूप के लिए SIMD निर्देश और एक थ्रेड सिंक्रनाइज़ेशन शामिल हैं। प्रक्रिया।

इस कोर वाला पहला प्रोसेसर 3.2 और 3.4 गीगाहर्ट्ज़ की आवृत्ति पर काम करेगा। उनके केस वर्तमान में पेंटियम 4 नॉर्थवुड प्रोसेसर में उपयोग किए जाने वाले केस के साथ संगत होंगे। भविष्य में, प्रेस्कॉट प्रोसेसर को 775 पिन वाले नए एलजीए 775 पैकेज में परिवर्तित किया जाएगा, जिसके लिए सॉकेट टी कनेक्टर के साथ नए मदरबोर्ड की भी आवश्यकता होगी।

नए कोर के आधार पर सेलेरॉन प्रोसेसर का उत्पादन भी जारी रहेगा। केवल अब यह बिल्कुल वैसा सेलेरॉन नहीं है जैसा पहले था। प्रेस्कॉट कोर पर आधारित सेलेरॉन चिप्स न केवल बढ़ी हुई कोर क्लॉक फ़्रीक्वेंसी के कारण नॉर्थवुड पर आधारित अपने पूर्ववर्तियों की तुलना में तेज़ होंगे। वे 533 मेगाहर्ट्ज की आवृत्ति के साथ एक सिस्टम बस का समर्थन करेंगे, और उनका कैश आकार 128 से 256 केबी तक बढ़ जाएगा। प्रेस्कॉट कोर पर आधारित पहले सेलेरॉन की आवृत्तियाँ 2.8 और 3.06 गीगाहर्ट्ज़ होंगी। अभी तक 90 एनएम तकनीक का उपयोग करने वाले प्रोसेसर जारी नहीं करने के बाद, इंटेल पहले से ही 65 एनएम मानकों के साथ चिप उत्पादन तकनीक की अगली पीढ़ी को पूरी तरह से विकसित कर रहा है। विकास भी चल रहा है, और न केवल 0.065 माइक्रोन का उपयोग करके बनाए गए कार्यशील चिप्स हैं। तकनीकी प्रक्रिया, लेकिन 45 एनएम, 32 एनएम और यहां तक कि 22 एनएम भी।

प्रेस्कॉट का अनुसरण कोर द्वारा किया जाएगा तेजस 1066 मेगाहर्ट्ज बस के साथ। इसके आधार पर 6 से 9.2 गीगाहर्ट्ज तक की क्लॉक फ्रीक्वेंसी वाले आठ अलग-अलग प्रोसेसर पेश किए जाएंगे। उनमें से पहला 2004 के अंत में बिक्री पर आने वाला है। इसके बाद कंपनी कोर पेश करेगी Nehalem, जो 1200 मेगाहर्ट्ज सिस्टम बस का उपयोग करता है और 10 गीगाहर्ट्ज से अधिक की ऑपरेटिंग आवृत्ति की अनुमति देता है। पूरी तरह से नेहेल्म पर आधारित होगी नई वास्तुकला. यह प्रेस्कॉट और तेजस की तरह उन्नत पेंटियम 4 नहीं होगा। यह लाग्रांडे हार्डवेयर सुरक्षा प्रणाली का उपयोग करेगा, और कुछ रिपोर्टों के अनुसार, यह अधिक उन्नत मल्टी-थ्रेडिंग तकनीक का उपयोग करेगा। चिप में ट्रांजिस्टर की संख्या लगभग 150-250 मिलियन होगी। पेंटियम नेहलेम 2005 में प्रदर्शित होना चाहिए।

हाल ही में पेंटियम 4 लाइन से एक नए प्रोसेसर की भी घोषणा की गई - इंटेल पेंटियम 4 एक्सट्रीम संस्करण.

यह हाइपर-थ्रेडिंग तकनीक से लैस है, 800 मेगाहर्ट्ज सिस्टम बस पर चलता है और इसकी कोर क्लॉक स्पीड 3.2 गीगाहर्ट्ज है। लेकिन पिछले पेंटियम 4 से इसका मुख्य अंतर चिप में एकीकृत 2 एमबी एल3 कैश मेमोरी की उपस्थिति थी! यह कैश मेमोरी मानक 512 केबी एल 2 कैश को पूरक करती है और प्रोसेसर कोर आवृत्ति पर भी काम करती है (हालांकि बहुत अधिक विलंबता के साथ, क्योंकि यह अतुल्यकालिक है और सबसे अधिक उपयोग किए जाने वाले क्षेत्रों से डेटा के साथ काम को तेज करने के लिए डिज़ाइन किया गया है) प्रणाली की याददाश्त). इस प्रकार, नए पेंटियम 4 एक्सट्रीम संस्करण की कुल कैश मेमोरी 2.5 एमबी है! यह एकमात्र डेस्कटॉप प्रोसेसर है जिसमें कोर में तीसरे स्तर का कैश एकीकृत है।

पेंटियम 4 एक्सट्रीम एडिशन प्रोसेसर इंटेल द्वारा मुख्य रूप से गेमिंग बाजार के लिए तैनात किया गया है, हालांकि उत्पादक वर्कस्टेशन में इसके उपयोग को बाहर नहीं रखा गया है। नया प्रोसेसर एकीकृत L3 कैश के साथ मल्टीप्रोसेसर Xeon MP के कोर का उपयोग करता है। इसे 800 मेगाहर्ट्ज सिस्टम बस का समर्थन करने, बिजली की खपत को कम करने आदि के लिए थोड़ा संशोधित किया गया था, और एक मानक पेंटियम 4 केस में पैक किया गया था।

इस सामग्री को लिखते समय, इंटरनेट साइटों से जानकारी का उपयोग किया गया था

एलेक्सी गैवरिलेंकोउर्फ [-एलेक्स-]

पेंटियम (उच्चारण पेंटियम) 22 मार्च 1993 से इंटेल कॉर्पोरेशन द्वारा निर्मित x86 परिवार माइक्रोप्रोसेसरों की कई पीढ़ियों का ट्रेडमार्क है। पेंटियम इंटेल का पांचवीं पीढ़ी का प्रोसेसर है और इंटेल 80486 (अक्सर इसे 486 के रूप में संदर्भित) की जगह लेता है।

I3(4)86 से अंतर:

- पिछले मॉडल की तुलना में एड्रेस मेमोरी नहीं बदली है;

- 64-बिट डेटा चैनल (यदि पेंटियम 32-बिट है);

- पहली बार, 2 पाइपलाइनें स्वतंत्र रूप से धाराओं को पढ़ती हैं और संसाधित करती हैं;

- आदेशों का सट्टा निष्पादन पहली बार सामने आया;

- पहली बार, आदेशों को स्वचालित रूप से पुनः व्यवस्थित करने जैसी तकनीक का उपयोग किया गया है:

बदले हुए आदेश का कोई असर नहीं है. लेकिन समस्या सशर्त छलांग है.

AX,BX जोड़ें CX,AX YZ M1 MOV DX जोड़ें, 5h

समाधान: यह माना जाता है कि संक्रमण पूरा हो गया है, इसलिए, कमांड को पाइपलाइन में पढ़ा गया है; यदि यह पता चलता है कि सब कुछ सही है, तो निष्पादन जारी रहता है, अन्यथा, पाइपलाइन को रीसेट कर दिया जाता है और संक्रमण बिंदु से रिबूट किया जाता है।

धारणा के कारण:

- संक्रमण आँकड़े (यदि अनेक हों तो एकाधिक चक्र);

- पूर्वानुमान ब्लॉक आँकड़ों का उपयोग करता है: यदि संक्रमण सशर्त है और पीछे की ओर इंगित करता है, तो इसके निष्पादित होने की संभावना है। (उदाहरण: तक दोहराएँ)। और अगर आगे बढ़ाया तो बहुत संभावना है कि वो पूरा नहीं होगा.

पहली बार, मल्टीप्रोसेसिंग के लिए हार्डवेयर समर्थन (एक विशेष बस/विशेष इंटरफ़ेस का उपयोग करके कनेक्शन)

(डेटा बस 32 ----> 64, 2 कन्वेयर के बाद से)

पेंटियम क्लॉक स्पीड: 60-150 मेगाहर्ट्ज एमएमएक्स क्लॉक स्पीड: 200 मेगाहर्ट्ज

अतिरिक्त रजिस्टर हैं जो कोड की शुरुआत के बाद से गुजरे घड़ी चक्रों की संख्या के लिए ज़िम्मेदार हैं।

एक कमांड सीपीयूआईडी - सीपीयू पहचानकर्ता है।

सभी प्रकार के रजिस्टर.

स्थापत्य विशेषता

(इस सीआईएससी से पहले) सीआईएससी शेल में सीआईएससी कमांड को आंतरिक आरआईएससी कोड में परिवर्तित करने के लिए एक आंतरिक ट्रांसकोडर है।

इंटरप्ट: पहले -> PIC (सॉफ्टवेयर इंटरप्ट कंट्रोलर)।

पहले, स्रोत प्रोसेसर लेग पर एक इंटरप्ट सिग्नल और ट्रांज़िशन पता था।

एपीआईसी: स्रोत - एक विशेष बस के माध्यम से आने वाला संदेश।

इंटेल पेंटियम P6200 प्रोसेसर

इंटेल पेंटियम P6200- प्रोसेसर प्रवेश के स्तर पर, लैपटॉप के लिए डिज़ाइन किया गया। यह 2.13 गीगाहर्ट्ज़ पर काम करता है, लेकिन दुर्भाग्य से टर्बोबूस्ट तकनीक का समर्थन नहीं करता है स्वचालित त्वरण. इसमें एईएस एन्क्रिप्शन और मल्टी-थ्रेडिंग समर्थन का भी अभाव है। सीपीयू उन्नत स्पीडस्टेप तकनीक का समर्थन करता है, जो कम प्रोसेसर लोड की अवधि के दौरान बिजली की खपत को कम करता है, लेकिन इस प्रोसेसर में (साथ ही पेन्रीन पेंटियम श्रृंखला में) अन्य बिजली-बचत प्रौद्योगिकियां अक्षम हैं।

P6200 Arrandale माइक्रोआर्किटेक्चर पर आधारित है, इसलिए इसमें एक एकीकृत मेमोरी नियंत्रक है चित्रोपमा पत्रकइंटेल एचडी ग्राफ़िक्स (दोनों 45 एनएम पर निर्मित तकनीकी प्रक्रिया, और सीपीयू 32 एनएम है)। अंतर्निहित GMA HD ग्राफिक्स कार्ड 500 मेगाहर्ट्ज पर संचालित होता है और टर्बो बूस्ट तकनीक की बदौलत 667 मेगाहर्ट्ज तक ओवरक्लॉक करने में सक्षम है।

कम क्लॉक स्पीड और टर्बो बूस्ट और हाइपरथ्रेडिंग की कमी के कारण इस प्रोसेसर का प्रदर्शन थोड़ा सीमित है। गीगाहर्ट्ज क्लॉक रेट के आधार पर, एकीकृत मेमोरी कंट्रोलर और मामूली कोर सुधारों के कारण पेंटियम पी6200 को समान क्लॉक किए गए कोर 2 डुओ से थोड़ा बेहतर होना चाहिए।

*संकेतित घड़ी की गति निर्माता द्वारा परिवर्तन के अधीन हो सकती है।पेंटियम प्रोसेसर का इतिहास

10 मई 1992 को रविवार की एक शांत सुबह, चार INTEL इंजीनियर सैन जोस अंतर्राष्ट्रीय हवाई अड्डे पर पहुंचे। वीडियो उपकरण स्थापित करने के बाद, एंजेला चांग, एरिक डेवैनैन, अवतार सैनी और सुहेल ज़ात्री घबराए हुए कमरे के चारों ओर घूम रहे थे, किसी भी क्षण ओरेगॉन से विमान का इंतजार कर रहे थे।

जब विमान के उतरने के कुछ मिनट बाद मार्क होपमैन एक छोटा नीला सूटकेस लेकर गलियारे से बाहर निकले, तो स्वागत करने वाला पूरा समूह उनकी ओर बढ़ गया। सारा ध्यान सूटकेस पर केंद्रित था, जिसमें 5 ओरेगॉन फैक्ट्री के डेवलपर्स का उत्पाद था। यह विश्वास करना कठिन था कि इस सूटकेस में कई लोगों के तीन साल के काम का नतीजा था, जो एक छोटी सी चिप में सन्निहित था। इस प्रकार पेंटियम प्रोसेसर का जीवन शुरू हुआ, जिसे औपचारिक रूप से 22 मार्च 1993 को पेश किया गया था।

जून 1989 में पेंटियम प्रोसेसर का विकास शुरू करते हुए जब विनोद डैम ने पहला स्केच बनाया, तो उन्हें इस बात का अंदाजा नहीं था कि यह विशेष उत्पाद INTEL की मुख्य उपलब्धियों में से एक होगा। पेंटियम प्रोसेसर के आगमन के साथ, कंप्यूटर बाजार तुरंत बदल गया और प्रतिस्पर्धा का एक नया चरण शुरू हुआ। सैन माइक्रोसिस्टम्स, एमआईपीएस और सुपर-फास्ट चिप्स विकसित करने वाले अन्य आरआईएससी प्रोसेसर विक्रेताओं ने स्पष्ट रूप से स्वीकार किया है कि इंटेल का नया प्रोसेसर नए डेस्कटॉप पीसी के लिए मानक बन जाएगा।

पेंटियम प्रोसेसर का जन्म आसान नहीं था

सिद्धांत के अनुसार, प्रोसेसर बनाते समय, विकास टीम एक डिज़ाइन अवधारणा बनाती है जो इसके मुख्य गुणों और नवाचारों को परिभाषित करती है। इसके बाद, इंजीनियर तर्क को डिज़ाइन करते हैं, जिसे फिर विशिष्ट सर्किट में लागू किया जाता है। एक बार सर्किट डिज़ाइन पूरा हो जाने पर, टोपोलॉजी डिज़ाइनर प्रत्येक ट्रांजिस्टर को खींचते हैं। उनके काम के परिणामस्वरूप, अंतिम खाका तैयार हुआ, वास्तव में, सब कुछ अलग था। तेज़ परियोजना वितरण की आवश्यकता को पूरा करने के लिए पारंपरिक डिज़ाइन प्रक्रिया को मौलिक रूप से नया रूप दिया गया।

जैसे ही विकास दल ने एक स्थानीय कार्य पूरा किया, प्रबंधकों ने संसाधनों का पुनर्वितरण कर दिया। प्रत्येक इंजीनियर ने एक व्यक्तिगत समस्या का समाधान किया। देरी और कठिनाइयों से टीम भावना की लगातार परीक्षा होती रही, लेकिन परियोजना की समय-सीमा इससे प्रभावित नहीं हुई। सभी कार्यों को पूरा करने के लिए कंप्यूटर-सहायता प्राप्त डिज़ाइन में नवीनतम प्रगति का उपयोग किया गया। 286, Intel386 और Intel486 प्रोसेसर में समान समस्याओं को डिजाइन करने और हल करने में प्राप्त अनुभव बहुत उपयोगी था।

जैसे ही परियोजना का अगला चरण पूरा हुआ, व्यापक परीक्षण की प्रक्रिया तुरंत शुरू हो गई। Intel486 के साथ उत्पन्न समस्याओं को न दोहराने की इच्छा थी, जिसके कारण इसके उत्पादन में लॉन्च में देरी हुई। प्रत्येक त्रुटि का पता लगाया गया और उसके कारणों को समाप्त कर दिया गया। शेष इंजीनियरों ने तर्क, वास्तुकला और समग्र डिजाइन को सत्यापित करने के लिए सैकड़ों परीक्षण किए। पेंटियम प्रोसेसर की वास्तुकला खोजने से पहले उन्होंने 5,000 से अधिक शोधन परीक्षण किए। परीक्षण के लिए, एक विशेष तकनीक विकसित की गई जिससे केबलों का उपयोग करके 14 बोर्डों पर जुड़े प्रोग्राम योग्य उपकरणों का उपयोग करके पेंटियम प्रोसेसर के कामकाज का अनुकरण करना संभव हो गया। केवल जब सभी त्रुटियों का पता चल गया, तो प्रोसेसर वास्तविक सिस्टम में काम करने में सक्षम हो गया। इसके अलावा, सभी प्रमुख डेवलपर्स ने पेंटियम प्रोसेसर के विकास और परीक्षण में सक्रिय भाग लिया व्यक्तिगत कम्प्यूटर्सऔर सॉफ़्टवेयर, जिसने परियोजना की समग्र सफलता में बहुत योगदान दिया।

1991 के अंत में, जब प्रोसेसर प्रोटोटाइप पूरा हो गया, तो इंजीनियर उस पर सॉफ्टवेयर चलाने में सक्षम हो गए। टोपोलॉजी को अनुकूलित करने और परिचालन दक्षता में सुधार करने के लिए डिजाइनरों ने माइक्रोस्कोप के तहत सब्सट्रेट की वायरिंग और सिग्नल प्रवाह का अध्ययन करना शुरू किया। डिज़ाइन काफी हद तक फरवरी 1992 में पूरा हुआ। प्रोसेसर के एक पायलट बैच का व्यापक परीक्षण शुरू हुआ, जिसके दौरान सभी ब्लॉक और नोड्स का परीक्षण किया गया। अप्रैल 1992 में, यह निर्णय लिया गया कि पेंटियम प्रोसेसर का व्यावसायिक विकास शुरू करने का समय आ गया है। ओरेगॉन फ़ैक्टरी 5 को मुख्य औद्योगिक आधार के रूप में चुना गया था।

अंततः 3 मिलियन से अधिक ट्रांजिस्टर को टेम्पलेट्स में स्थानांतरित कर दिया गया। उत्पादन का औद्योगिक विकास और तकनीकी विशेषताओं की फाइन-ट्यूनिंग शुरू हुई, जो 10 महीने बाद, 22 मार्च, 1993 को पेंटियम प्रोसेसर की विस्तृत प्रस्तुति के साथ समाप्त हुई।

INTEL की आधुनिक माइक्रोप्रोसेसर तकनीक

सेमीकंडक्टर डिजाइन और विनिर्माण की कला में इंटेल की प्रगति से छोटे पैकेजों में शक्तिशाली माइक्रोप्रोसेसर का उत्पादन संभव हो रहा है। माइक्रोप्रोसेसर डिजाइनर वर्तमान में उप-माइक्रोन रिज़ॉल्यूशन के साथ पूरक धातु ऑक्साइड सेमीकंडक्टर (सीएमओएस) प्रक्रिया प्रौद्योगिकी के साथ काम कर रहे हैं।

सबमाइक्रोन तकनीक का उपयोग इंटेल डेवलपर्स को प्रत्येक सब्सट्रेट पर अधिक ट्रांजिस्टर लगाने की अनुमति देता है। इससे X86 परिवार के लिए ट्रांजिस्टर की संख्या 8086 प्रोसेसर में 29,000 से बढ़ाकर Intel486 DX2 प्रोसेसर में 1.2 मिलियन करना संभव हो गया, जो पेंटियम प्रोसेसर में उच्चतम उपलब्धि है। 0.8 माइक्रोन BiCMOS तकनीक का उपयोग करके निर्मित, इसमें 3.1 मिलियन ट्रांजिस्टर हैं। BiCMOS प्रौद्योगिकी दो प्रौद्योगिकियों के लाभों को जोड़ती है: द्विध्रुवी (गति) और CMOS (कम बिजली की खपत)। Intel486 की तुलना में पेंटियम प्रोसेसर में दोगुने से अधिक ट्रांजिस्टर का उपयोग करके, डेवलपर्स ने उन घटकों को सब्सट्रेट पर रखा जो पहले प्रोसेसर के बाहर स्थित थे। अंदर घटक होने से पहुंच का समय कम हो जाता है, जिससे प्रदर्शन में उल्लेखनीय वृद्धि होती है। इंटेल की 0.8 माइक्रोन तकनीक तीन-परत धातु का उपयोग करती है और Intel486 प्रोसेसर में उपयोग की जाने वाली मूल 1.0 माइक्रोन दो-परत धातु तकनीक से बेहतर है।

इंटेल ने वैज्ञानिक और इंजीनियरिंग वर्कस्टेशन में उपयोग किए जाने वाले वैकल्पिक आर्किटेक्चर के बराबर लाभ प्राप्त करने के लिए माइक्रोप्रोसेसर डिजाइन प्रौद्योगिकी में नवीनतम प्रगति का लाभ उठाया, जबकि X86 श्रृंखला माइक्रोप्रोसेसर परिवार पर निर्मित 50 बिलियन डॉलर मूल्य के सॉफ्टवेयर के साथ संगतता सुनिश्चित की।

और पेंटियम प्रोसेसर के लिए सॉफ्टवेयर स्वयं नई तकनीक का उपयोग करके विकसित किया गया था। प्रोसेसर हार्डवेयर को डिजाइन करने के चरण में भी, ऑपरेटिंग सिस्टम और कंपाइलर विकसित करने वाली सभी प्रमुख कंपनियों - माइक्रोसॉफ्ट, आईबीएम, नेक्स्ट, बोरलैंड, वाटकॉम, मेटावेयर आदि के विशेषज्ञ इस परियोजना में शामिल होने लगे कॉर्पोरेट शैली मानक सॉफ़्टवेयर प्रदाताओं को ध्यान में रखते हुए, हार्डवेयर स्तर पर नई प्रोग्रामिंग प्रौद्योगिकियाँ। दूसरी ओर, नए प्रोसेसर के जन्म से पहले भी, X86 आर्किटेक्चर के विशिष्ट लाभों को प्रकट करने के लिए शास्त्रीय और विशेष अनुकूलन विधियों का उपयोग किया गया था, उदाहरण के लिए, लोड-राइट कमांड का उपयोग, शक्तिशाली एड्रेसिंग मोड, अपरिवर्तनीय कोड को हटाना लूप आदि से अनुभाग अब, केवल पारंपरिक अनुप्रयोगों को पुन: संकलित करके, नए प्रोसेसर पर उनके प्रदर्शन को दोगुना करना संभव है। यह फिलहाल ऐसा कुछ नहीं है जिसे INTEL का कोई भी प्रतिस्पर्धी पेश कर सके।

इंटेल प्रोसेसर की नई पीढ़ी

एक एकल सिलिकॉन सब्सट्रेट पर 3.1 मिलियन से अधिक ट्रांजिस्टर का संयोजन, 32-बिट पेंटियम प्रोसेसर 60 और 66 मेगाहर्ट्ज की क्लॉक स्पीड के साथ उच्च प्रदर्शन प्रदान करता है। इसका सुपरस्केलर आर्किटेक्चर उन्नत डिजाइन तकनीकों का उपयोग करता है जो प्रति घड़ी चक्र में एक से अधिक निर्देशों को निष्पादित करने की अनुमति देता है, जिसके परिणामस्वरूप पेंटियम किसी भी अन्य माइक्रोप्रोसेसर की तुलना में बड़ी मात्रा में पीसी-संगत सॉफ़्टवेयर को तेजी से चलाने में सक्षम होता है। मौजूदा सॉफ़्टवेयर क्षमताओं के अलावा, पेंटियम प्रोसेसर की उच्च-प्रदर्शन फ़्लोटिंग-पॉइंट अंकगणितीय इकाई मूल रूप से वर्कस्टेशन प्लेटफ़ॉर्म के लिए डिज़ाइन किए गए पहले से अनुपलब्ध तकनीकी और वैज्ञानिक अनुप्रयोगों का समर्थन करने के लिए बढ़ी हुई प्रसंस्करण शक्ति प्रदान करती है। जिस तरह स्थानीय और विस्तृत क्षेत्र नेटवर्क मेनफ्रेम कंप्यूटर द्वारा संचालित विरासती पदानुक्रमित नेटवर्क को प्रतिस्थापित करना जारी रखते हैं, पेंटियम प्रोसेसर के मल्टीप्रोसेसिंग लाभ और ऑपरेटिंग सिस्टम लचीलापन आज के औद्योगिक क्लाइंट-सर्वर अनुप्रयोगों के लिए आदर्श होस्ट कंप्यूटर हैं।

क्योंकि पेंटियम प्रोसेसर आज के हाई-एंड वर्कस्टेशन के बराबर या उससे अधिक प्रदर्शन स्तर प्राप्त करने में सक्षम है, यह ऐसे लाभ प्रदान करता है जिनकी पारंपरिक वर्कस्टेशन में कमी है: 50,000 से अधिक के साथ पूर्ण अनुकूलता सॉफ़्टवेयर एप्लिकेशनअरबों डॉलर की लागत से, जो INTEL की वास्तुकला के तहत लिखे गए थे। इसके अलावा, पेंटियम प्रोसेसर आज के डेस्कटॉप, वर्कस्टेशन और सर्वर पर उपलब्ध सभी प्रमुख ऑपरेटिंग सिस्टम का समर्थन करता है, जिसमें UNIX, Windows-NT, OS/2, सोलारिस और NEXTstep शामिल हैं।

पेंटियम प्रोसेसर. तकनीकी नवाचार

उच्च प्रदर्शन, अनुकूलता, डेटा एकीकरण और स्केलेबिलिटी के अनूठे संयोजन के रूप में कई नवाचार पेंटियम प्रोसेसर की एक विशिष्ट विशेषता हैं। यह भी शामिल है:

- सुपरस्केलर आर्किटेक्चर;

- प्रोग्राम कोड और डेटा की अलग कैशिंग;

- सही जंप पता भविष्यवाणी ब्लॉक;

- उच्च प्रदर्शन फ़्लोटिंग पॉइंट इकाई;

- विस्तारित 64-बिट डेटा बस;

- मल्टीप्रोसेसर ऑपरेशन के लिए समर्थन;

- मेमोरी पेज का आकार निर्धारित करने के साधन;

- त्रुटि का पता लगाने और कार्यात्मक अतिरेक उपकरण;

- निष्पादन प्रबंधन;

- इंटेल ओवरड्राइव प्रोसेसर के साथ स्केलेबल।

पेंटियम प्रोसेसर आर्किटेक्चर

1 - 64-बिट बस इंटरफ़ेस;

2 - प्रोग्राम कोड कैशिंग उपकरण;

3 - प्रीफ़ेच बफ़र्स;

4 - 32-बिट पूर्णांक ALU इकाई;

5 - 32-बिट पूर्णांक ALU इकाई;

6 - रजिस्टरों का सेट;

7 - डेटा कैशिंग उपकरण;

8 - सही संक्रमण पते की भविष्यवाणी के लिए ब्लॉक;

9 - कन्वेयर फ्लोटिंग पॉइंट गणना का ब्लॉक।

सुपरस्केलर वास्तुकला

पेंटियम प्रोसेसर का सुपरस्केलर आर्किटेक्चर एक इंटेल-ओनली, डुअल-पाइप औद्योगिक आर्किटेक्चर है जो प्रोसेसर को प्रति घड़ी चक्र में एक से अधिक निर्देश निष्पादित करके प्रदर्शन के नए स्तर प्राप्त करने की अनुमति देता है। शब्द "सुपरस्केलर" एक माइक्रोप्रोसेसर आर्किटेक्चर को संदर्भित करता है जिसमें एक से अधिक कंप्यूटिंग इकाइयाँ होती हैं। ये कंप्यूटिंग इकाइयाँ, या पाइपलाइन, वे नोड हैं जहाँ सभी प्रमुख डेटा और कमांड प्रोसेसिंग होती है।

पेंटियम प्रोसेसर के सुपरस्केलर आर्किटेक्चर का उद्भव इंटेल के 32-बिट आर्किटेक्चर वाले प्रोसेसर के पिछले परिवार का एक स्वाभाविक विकास है। उदाहरण के लिए, Intel486 प्रोसेसर एक घड़ी चक्र में अपने कई निर्देशों को निष्पादित करने में सक्षम है, लेकिन INTEL प्रोसेसर के पिछले परिवारों को एक निर्देश को निष्पादित करने के लिए कई घड़ी चक्रों की आवश्यकता होती है।

एक ही घड़ी चक्र में कई निर्देशों को निष्पादित करने की क्षमता मौजूद है क्योंकि पेंटियम प्रोसेसर में दो पाइपलाइन हैं जो एक साथ दो निर्देशों को निष्पादित कर सकती हैं। सिंगल-पाइप Intel486 की तरह ही, डुअल-पाइप पेंटियम प्रोसेसर भी कार्य करता है सरल आदेशपांच चरणों में: पूर्व-प्रशिक्षण, पहला डिकोडिंग (निर्देश डिकोडिंग), दूसरा डिकोडिंग (पता निर्माण), निष्पादन और पोस्टबैक। यह कई आदेशों को निष्पादन के विभिन्न चरणों में रखने की अनुमति देता है, जिससे कम्प्यूटेशनल प्रदर्शन बढ़ता है।

प्रत्येक पाइपलाइन की अपनी अंकगणित तर्क इकाई (एएलयू), पता पीढ़ी उपकरणों का एक सेट और एक डेटा कैशिंग इंटरफ़ेस होता है। Intel486 प्रोसेसर की तरह, पेंटियम प्रोसेसर हार्डवेयर निर्देश निष्पादन का उपयोग करता है, जो माइक्रोप्रोसेसरों के पिछले परिवारों में उपयोग किए गए कई माइक्रोनिर्देशों को प्रतिस्थापित करता है। इन निर्देशों में लोड, स्टोर और सरल ALU ऑपरेशन शामिल हैं जिन्हें प्रोसेसर हार्डवेयर द्वारा माइक्रोकोड की आवश्यकता के बिना निष्पादित किया जा सकता है। यह अनुकूलता को प्रभावित किए बिना प्रदर्शन में सुधार करता है। अधिक जटिल कमांड निष्पादित करते समय, पेंटियम प्रोसेसर के विस्तारित माइक्रोकोड के निष्पादन प्रदर्शन को और तेज करने के लिए दोनों सुपरस्केलर आर्किटेक्चर पाइपलाइनों का उपयोग किया जाता है।

इन वास्तुशिल्प नवाचारों के परिणामस्वरूप, पिछले माइक्रोप्रोसेसरों की तुलना में, समान समय में काफी बड़ी संख्या में निर्देश निष्पादित किए जा सकते हैं।

प्रोग्राम कोड और डेटा की अलग कैशिंग

पेंटियम प्रोसेसर में लागू किया गया एक और प्रमुख क्रांतिकारी सुधार स्प्लिट कैशिंग की शुरूआत है। कैशिंग अक्सर उपयोग किए जाने वाले कोड और तेज़ मेमोरी से प्राप्त डेटा के लिए अस्थायी भंडारण प्रदान करके प्रदर्शन में सुधार करता है, जब संभव हो तो कुछ कमांड के लिए बाहरी सिस्टम मेमोरी तक पहुंच को प्रतिस्थापित करता है। उदाहरण के लिए, Intel486 प्रोसेसर में ऑन-चिप कैश मेमोरी का एक 8-KB ब्लॉक होता है जिसका उपयोग प्रोग्राम कोड और डेटा दोनों को कैश करने के लिए किया जाता है।

इंटेल डिजाइनरों ने पेंटियम प्रोसेसर के 3.1 मिलियन ट्रांजिस्टर (तुलना के लिए, इंटेल 486 में 1.2 मिलियन ट्रांजिस्टर होते हैं) पर बने एक अतिरिक्त सर्किट का उपयोग करके प्रोग्राम कोड और डेटा की अलग आंतरिक कैशिंग बनाकर इस सीमा को पार कर लिया। यह बस विवाद को समाप्त करके प्रदर्शन में सुधार करता है और दोहरी कैशिंग को पहले की तुलना में अधिक बार उपलब्ध कराता है। उदाहरण के लिए, चरण के दौरान प्रारंभिक तैयारी, कमांड कैश से प्राप्त कमांड कोड का उपयोग किया जाता है। एकल कैश ब्लॉक के मामले में, कमांड तैयारी प्रक्रिया और डेटा एक्सेस के बीच विरोध हो सकता है। कमांड और डेटा के लिए अलग-अलग कैशिंग करने से दोनों कमांड को एक साथ निष्पादित करने की अनुमति देकर ऐसे टकराव समाप्त हो जाते हैं। पेंटियम प्रोसेसर के कोड और डेटा कैश में प्रत्येक में 8 केबी की जानकारी होती है, और प्रत्येक को दो-तरफा कैश-एसोसिएटिव कैश के सेट के रूप में व्यवस्थित किया जाता है - केवल पूर्वावलोकन किए गए निर्दिष्ट 32-बाइट सेगमेंट को लिखने के लिए डिज़ाइन किया गया है, जो बाहरी कैश की तुलना में तेज़ है। इन सभी प्रदर्शन संवर्द्धन के लिए 64-बिट आंतरिक डेटा बस के उपयोग की आवश्यकता होती है, जो डाउनस्ट्रीम डेटा लोड करते समय दोहरी कैशिंग और सुपरस्केलर पाइपलाइनिंग की अनुमति देता है। डेटा कैश में दो इंटरफ़ेस होते हैं, प्रत्येक पाइपलाइन के लिए एक, जो इसे एक ही मशीन चक्र के भीतर दो अलग-अलग निर्देशों को डेटा प्रदान करने की अनुमति देता है। कैश से डेटा पुनर्प्राप्त होने के बाद, इसे राइट-बैक मोड में मुख्य मेमोरी में लिखा जाता है। यह कैशिंग तकनीक देती है बेहतर प्रदर्शनसरल डायरेक्ट-राइट कैशिंग की तुलना में, जिसमें प्रोसेसर कैश और मुख्य मेमोरी में एक साथ डेटा लिखता है। हालाँकि, पेंटियम प्रोसेसर केवल-लेखन कैशिंग का समर्थन करने के लिए स्वयं को गतिशील रूप से कॉन्फ़िगर करने में सक्षम है।

इस प्रकार, डेटा कैशिंग दो अलग-अलग महान समाधानों का उपयोग करता है: एक राइट-बैक कैश और एक एल्गोरिदम जिसे एमईएसआई (संशोधित करें, बहिष्कृत करें, आवंटित करें, हटाएं) प्रोटोकॉल कहा जाता है। राइट-बैक कैश आपको पहले उपयोग किए गए प्रत्यक्ष सरल कैशिंग के विपरीत, मुख्य मेमोरी तक पहुंच के बिना कैश में लिखने की अनुमति देता है।

ये समाधान पुन: डिज़ाइन की गई बस का उपयोग करके और सिस्टम में आने वाली बाधाओं को सक्रिय रूप से समाप्त करके उत्पादकता बढ़ाते हैं। बदले में, एमईएसआई प्रोटोकॉल कैश मेमोरी में डेटा की अनुमति देता है बाह्य स्मृतिउन्नत मल्टीप्रोसेसर सिस्टम में मैच एक उत्कृष्ट समाधान है, जहां विभिन्न प्रोसेसर समान डेटा साझा कर सकते हैं।

उच्च प्रदर्शन फ़्लोटिंग पॉइंट इकाई

32-बिट सॉफ्टवेयर अनुप्रयोगों के बढ़ते ज्वार में कई गणना-गहन, ग्राफिक्स-आधारित प्रोग्राम शामिल हैं जो गणितीय गणना करने वाले फ्लोटिंग-पॉइंट ऑपरेशन करने के लिए बहुत सारे सीपीयू संसाधनों का उपभोग करते हैं। जैसे-जैसे फ़्लोटिंग-पॉइंट सॉफ़्टवेयर द्वारा व्यक्तिगत कंप्यूटरों पर लगाई जाने वाली माँगें लगातार बढ़ती जा रही हैं, माइक्रोप्रोसेसर प्रौद्योगिकी में सुधार इन माँगों को पूरा कर सकता है। उदाहरण के लिए, Intel486 DX प्रोसेसर, गणित सहप्रोसेसर के साथ एक ही सब्सट्रेट पर एकीकृत पहला माइक्रोप्रोसेसर था। INTEL प्रोसेसर के पिछले परिवारों में, जब फ़्लोटिंग पॉइंट गणनाओं का उपयोग करना आवश्यक होता था, तो बाहरी गणितीय सहप्रोसेसर का उपयोग किया जाता था।

पेंटियम प्रोसेसर एक उन्नत अंतर्निर्मित फ़्लोटिंग-पॉइंट इकाई के उपयोग के माध्यम से उच्च-स्तरीय गणित गणनाओं को सक्षम बनाता है जिसमें आठ-चक्र पाइपलाइन और हार्डवेयर-आधारित कोर गणित फ़ंक्शन शामिल हैं। चार-चक्र फ़्लोटिंग पॉइंट निर्देश पाइपलाइनें चार-चक्र पूर्णांक पाइपलाइन की पूरक हैं। अधिकांश फ़्लोटिंग पॉइंट निर्देशों को एक पूर्णांक पाइपलाइन में निष्पादित किया जा सकता है और फिर फ़्लोटिंग पॉइंट पाइपलाइन में फीड किया जा सकता है। गणनाओं को गति देने के लिए हार्डवेयर में जोड़, गुणा और भाग जैसे सामान्य फ़्लोटिंग पॉइंट फ़ंक्शंस लागू किए जाते हैं।

इन नवाचारों के परिणामस्वरूप, पेंटियम प्रोसेसर 33-मेगाहर्ट्ज इंटेल 486 डीएक्स की तुलना में फ्लोटिंग-पॉइंट निर्देशों को पांच गुना तेजी से निष्पादित करता है, जो उन्हें सीएडी और 3 डी ग्राफिक्स जैसे उन्नत वीडियो अनुप्रयोगों के अभिन्न अंग उच्च गति संख्यात्मक गणना के लिए अनुकूलित करता है।

66 मेगाहर्ट्ज पेंटियम प्रोसेसर 64.5 की SPECint92 रेटिंग के साथ एक नंबर क्रंचर की तरह प्रदर्शन करता है, जो लगभग डिजिटल के अल्फा आरआईएससी प्रोसेसर जितना अच्छा है, लेकिन दोगुनी तेजी से चलता है।

पेंटियम प्रोसेसर का समग्र प्रदर्शन 25 मेगाहर्ट्ज Intel486 SX से 6 गुना बेहतर और 66 मेगाहर्ट्ज Intel486 DX2 से 2.6 गुना बेहतर है। 66 मेगाहर्ट्ज पेंटियम प्रोसेसर के लिए iCOMP रेटिंग इंडेक्स, जो प्रति सेकंड 112 मिलियन ऑपरेशन करता है, 567 है। iCOMP (Intel COmparative Microprocessor Peformance) इंडेक्स INTEL के 32-बिट प्रोसेसर के प्रदर्शन की सापेक्ष तुलना करता है।

विस्तारित 64-बिट डेटा बस

पेंटियम प्रोसेसर बाहर से एक 32-बिट डिवाइस है। मेमोरी में बाहरी डेटा बस 64-बिट है, जो प्रति बस चक्र में स्थानांतरित डेटा की मात्रा को दोगुना कर देती है। पेंटियम प्रोसेसर कई प्रकार के बस चक्रों का समर्थन करता है, जिसमें बर्स्ट मोड भी शामिल है, जो 256 बिट्स से डेटा कैश में और एक ही बस चक्र के भीतर डेटा को फोड़ता है।

डेटा बस मुख्य राजमार्ग है जो प्रोसेसर और मेमोरी सबसिस्टम के बीच सूचना स्थानांतरित करता है। इस 64-बिट डेटा बस के लिए धन्यवाद, पेंटियम प्रोसेसर Intel486 DX प्रोसेसर पर स्थानांतरण गति में काफी सुधार करता है - 66 मेगाहर्ट्ज प्रोसेसर के लिए 528 एमबी/सेकंड, जबकि 50 मेगाहर्ट्ज Intel486 DX प्रोसेसर के लिए 160 एमबी/सेकंड। यह उन्नत डेटा बस सुपरस्केलर प्रोसेसिंग यूनिट के एक साथ निर्देश और डेटा फीडिंग का समर्थन करके उच्च गति कंप्यूटिंग की सुविधा प्रदान करती है, जो Intel486 DX प्रोसेसर की तुलना में और भी अधिक समग्र पेंटियम प्रोसेसर प्रदर्शन प्रदान करती है।

सामान्य तौर पर, व्यापक डेटा बस होने के कारण, पेंटियम प्रोसेसर बस चक्रों की पाइपलाइनिंग प्रदान करता है, जो बस थ्रूपुट को बढ़ाने में मदद करता है। पाइपलाइनिंग बस चक्र पहले चक्र के निष्पादन पूरा होने से पहले दूसरे चक्र को शुरू करने की अनुमति देता है। इससे मेमोरी सबसिस्टम को पते को डीकोड करने के लिए अधिक समय मिलता है, जिससे धीमे, कम महंगे मेमोरी घटकों का उपयोग करने की अनुमति मिलती है, जिसके परिणामस्वरूप समग्र सिस्टम लागत कम होती है। पढ़ने और लिखने की प्रक्रियाओं में तेजी, पता और डेटा समानता, और एकल-चक्र डिकोडिंग सभी मिलकर थ्रूपुट में सुधार करते हैं और सिस्टम क्षमताओं को बढ़ाते हैं।

बहु

पेंटियम प्रोसेसर मल्टीप्रोसेसर सिस्टम की बढ़ती लहर के लिए आदर्श है और आधुनिक कंप्यूटिंग में उच्चतम स्तर का प्रदर्शन और प्रसंस्करण शक्ति प्रदान करता है। मल्टीप्रोसेसर एप्लिकेशन जो दो या दो से अधिक पेंटियम प्रोसेसर को जोड़ते हैं, उन्हें उन्नत सिलिकॉन आर्किटेक्चर, अलग-अलग ऑन-चिप कोड और डेटा कैशिंग, बाहरी कैश प्रबंधन के लिए चिपसेट और परिष्कृत डेटा अखंडता नियंत्रण द्वारा अच्छी तरह से परोसा जाता है।

जैसा कि पहले चर्चा की गई है, पेंटियम प्रोसेसर अपने MESI प्रोटोकॉल के साथ कैश-ऑर्डर किए गए कैश का समर्थन करता है। जब एक प्रोसेसर दूसरे प्रोसेसर में कैश्ड डेटा तक पहुंचता है, तो उसमें सही डेटा प्राप्त करने की क्षमता होती है। और यदि डेटा को संशोधित किया गया है, तो सभी प्रोसेसर के पास संशोधित रूप में डेटा प्राप्त करने की पहुंच है। इंटेल का नवीनतम पेंटियम प्रोसेसर यह भी निर्धारित करता है कि उपयोग की गई प्रोग्रामिंग विधि के आधार पर सिस्टम द्वारा कौन से कमांड पहचाने जाते हैं। यह आपको बहुत विशिष्ट तरीके से बताता है कि एकल-प्रोसेसर सिस्टम के लिए विकसित सॉफ़्टवेयर मल्टीप्रोसेसर वातावरण में कैसे सही ढंग से काम कर सकता है।

स्मृति को पृष्ठों में विभाजित करने का साधन

पेंटियम प्रोसेसर किसी भी पारंपरिक मेमोरी पेज आकार - 4 केबी या व्यापक, 4 एमबी पेजों का समर्थन करने के लिए विकल्प प्रदान करता है। यह विकल्प आपको जटिल रूप से पेज स्वैपिंग की आवृत्ति की गणना करने की अनुमति देता है ग्राफ़िक्स अनुप्रयोग, फ़्रेम बफ़र्स, और कर्नेल ऑपरेटिंग सिस्टम, जहां बढ़ा हुआ पृष्ठ आकार अब उपयोगकर्ताओं को प्रारंभ में बोझिल वस्तुओं का व्यापक आकार बदलने की अनुमति देता है। अधिक पृष्ठों के परिणामस्वरूप प्रदर्शन में वृद्धि होती है, जो सभी एप्लिकेशन सॉफ़्टवेयर में परिलक्षित होता है।

त्रुटि का पता लगाना और कार्यात्मक अतिरेक

आधुनिक क्लाइंट-सर्वर वातावरण के प्रसार के कारण डेटा हानि-महत्वपूर्ण अनुप्रयोगों में अच्छी डेटा सुरक्षा और आंतरिक माध्यमों से इसकी अखंडता सुनिश्चित करना महत्वपूर्ण होता जा रहा है। पेंटियम प्रोसेसर में मेनफ्रेम क्लास डिज़ाइन के पारंपरिक दो संवर्द्धन शामिल हैं - आंतरिक त्रुटि का पता लगाना और कार्यात्मक अतिरेक नियंत्रण (एफसीआर) - जो आज के विकसित डेस्कटॉप-आधारित सिस्टम में डेटा अखंडता सुनिश्चित करने में मदद करते हैं।

आंतरिक त्रुटि का पता लगाना आंतरिक कोड और डेटा कैशिंग, शिफ्ट टेबल एसोसिएशन, माइक्रोकोड और लक्ष्य जंप बफर को समता बिट के साथ पूरक करता है ताकि त्रुटियों का पता लगाने में मदद मिल सके जो उपयोगकर्ता और सिस्टम दोनों के लिए अदृश्य है। साथ ही, कार्यात्मक अतिरेक के माध्यम से नियंत्रण को डेटा हानि वाले महत्वपूर्ण अनुप्रयोगों के लिए अनुकूलित किया जाता है जहां पेंटियम प्रोसेसर मास्टर/पर्यवेक्षक कॉन्फ़िगरेशन में काम कर सकता है। यदि दो प्रोसेसरों के बीच असहमति का पता चलता है, तो सिस्टम को एक त्रुटि की सूचना दी जाती है। परिणामस्वरूप, 99% से अधिक त्रुटियाँ पाई जाती हैं।

इसके अलावा, एक एकीकृत परीक्षण उपकरण प्रोसेसर सब्सट्रेट पर स्थित है। स्व-परीक्षण 70% से अधिक पेंटियम प्रोसेसर नोड्स को कवर करता है, इसके लिए डाई रीसेट की आवश्यकता नहीं होती है, और यह आमतौर पर सिस्टम डायग्नोस्टिक्स में उपयोग की जाने वाली प्रक्रिया है। अन्य अंतर्निहित समाधानों में आईईईई 1149.1 मानक का कार्यान्वयन शामिल है जो प्रोसेसर के बाहरी कनेक्शन के परीक्षण की अनुमति देता है और एक डिबग मोड जो सॉफ़्टवेयर को प्रोसेसर के रजिस्टरों और स्थिति को देखने की अनुमति देता है।

निष्पादन प्रबंधन

प्रदर्शन प्रबंधन पेंटियम प्रोसेसर की एक विशेषता है जो सिस्टम और एप्लिकेशन एक्सटेंशन डेवलपर्स को अपने हार्डवेयर को अनुकूलित करने की अनुमति देता है सॉफ़्टवेयरसंभावित कोड बाधाओं की पहचान करके। और कार्यकर्ता आंतरिक प्रोसेसर घटनाओं जैसे पढ़ने और लिखने के प्रदर्शन, हिट और मिस कैशिंग, इंटरप्ट और बस उपयोग के लिए घड़ी चक्रों को देख और पढ़ सकते हैं। यह उन्हें दोहरे पेंटियम प्रोसेसर आर्किटेक्चर और उनके उत्पादों में कोड की दक्षता को मापने और इष्टतम प्रदर्शन के लिए उनके अनुप्रयोगों या सिस्टम को ठीक करने की अनुमति देता है। अंतिम उपयोगकर्ताओं के लिए लाभ बढ़ा हुआ लाभ है और शीर्ष प्रदर्शन, और यह सब पेंटियम प्रोसेसर, उपयोगकर्ता प्रणाली और एप्लिकेशन सॉफ़्टवेयर के साथ अच्छे इंटरैक्शन के लिए धन्यवाद है।

डेवलपर्स को पावर प्रबंधन, सुरक्षा और अन्य सुविधाओं के साथ सिस्टम डिजाइन करने में सक्षम बनाने के लिए, पेंटियम प्रोसेसर समान सिस्टम प्रबंधन मोड (एसएमएम) का समर्थन करते हैं इंटेल वास्तुकलाएस.एल.

अनुमापकता

INTEL के 32-बिट माइक्रोप्रोसेसर आर्किटेक्चर में जो कुछ भी नया है, उसके साथ-साथ, पेंटियम प्रोसेसर को INTEL के स्टैकेबल आर्किटेक्चर का उपयोग करके आसानी से विस्तार योग्य बनाया गया है। ये नवाचार प्रदर्शन संवर्द्धन के साथ उपयोगकर्ताओं के निवेश की रक्षा करते हैं जो व्यक्तिगत घटकों के जीवनकाल से परे इंटेल प्रोसेसर आर्किटेक्चर पर आधारित सिस्टम की उत्पादकता को बनाए रखने में मदद करते हैं। स्टैकेबल तकनीक एकल-चिप प्रदर्शन स्केलेबिलिटी की सरल स्थापना के साथ मौजूदा सिस्टम में सबसे उन्नत प्रोसेसर प्रौद्योगिकियों का लाभ उठाना संभव बनाती है। उदाहरण के लिए, पहला विस्तार समाधान ओवरड्राइव प्रोसेसर है, जिसे Intel486 SX और Intel486 DX प्रोसेसर के लिए डिज़ाइन किया गया है, जो Intel486 DX2 माइक्रोप्रोसेसरों के विकास में उपयोग की जाने वाली सरल क्लॉक-डबलिंग तकनीक का उपयोग करता है।

अधिकांश Intel486 मदरबोर्ड पर केंद्रीय माइक्रोप्रोसेसर के पास स्थित सॉकेट में इन अतिरिक्त प्रोसेसर में से एक को स्टैक करके, उपयोगकर्ता लगभग सभी सॉफ़्टवेयर अनुप्रयोगों के लिए समग्र सिस्टम प्रदर्शन को 70% से अधिक बढ़ा सकते हैं।

भविष्य में उन्नत तकनीक का उपयोग करके प्रोसेसर स्थापित करके पेंटियम प्रोसेसर परिवार पर आधारित सिस्टम के लिए ओवरड्राइव प्रोसेसर का उपयोग करके प्रौद्योगिकी को अपग्रेड करना भी संभव है। बदले में, पेंटियम प्रोसेसर तकनीक इसका आधार है अतिरिक्त प्रोसेसर, Intel486 DX2 पर आधारित सिस्टम के लिए विकसित किया गया।

इंटेल के पेंटियम प्रोसेसर x86 प्रोसेसर की पांचवीं पीढ़ी का प्रतिनिधित्व करते हैं। बुनियादी रजिस्टर आर्किटेक्चर और निर्देश सेट के संदर्भ में, वे ऊपर वर्णित 32-बिट प्रोसेसर के साथ संगत हैं, लेकिन उनके पास 64-बिट डेटा बस है, यही कारण है कि उन्हें कभी-कभी गलती से 64-बिट कहा जाता है। पिछली पीढ़ियों की तुलना में, पेंटियम प्रोसेसर में निम्नलिखित गुणात्मक अंतर हैं:

- सुपरस्केलर आर्किटेक्चर: प्रोसेसर में दो समानांतर प्रोसेसिंग पाइपलाइन (यू-पाइपलाइन) हैं पूरा स्थिरनिर्देश और कुछ हद तक सीमित सेट के साथ एक वी-पाइप), जिसकी बदौलत यह एक साथ दो निर्देशों को निष्पादित करने में सक्षम है। हालाँकि, इस आर्किटेक्चर के लाभ पूरी तरह से केवल एक विशेष सॉफ्टवेयर संकलन मोड के साथ ही महसूस होते हैं।

- एक समर्पित आंतरिक 8 केबी अनुदेश कैश के साथ संयोजन में गतिशील शाखा भविष्यवाणी तकनीक का उपयोग अधिकतम पाइपलाइन उपयोग सुनिश्चित करता है।

- 486 के विपरीत, केबी तक की क्षमता वाला आंतरिक (स्तर 1) डेटा कैश विलंबित (बाहरी बस मुक्त होने तक) लिखने के साथ काम करता है और प्रोटोकॉल का समर्थन करते हुए राइट-थ्रू या राइट-बैक मोड के लिए कॉन्फ़िगर किया गया है।

- प्रदर्शन में सुधार के लिए, बाहरी डेटा बस 64-बिट चौड़ी है, जिसके लिए उपयुक्त मेमोरी संगठन की आवश्यकता होती है।

- अंतर्निहित कोप्रोसेसर, वास्तुशिल्प सुधार (पाइपलाइनिंग) के कारण, प्रदर्शन में एफपीयू-486 से 2-10 गुना तेज है।

- सीपीयू परिवार और मॉडल की पहचान सहित कई नए निर्देश पेश किए गए हैं।

- आंतरिक उपकरणों (आंतरिक समता नियंत्रण) और बाहरी बस इंटरफ़ेस की त्रुटि का पता लगाने को लागू किया जाता है, पता बस की समता की निगरानी की जाती है।

- कार्यात्मक रूप से निरर्थक दोहरे प्रोसेसर सिस्टम के निर्माण की संभावना पेश की गई है।

- सममित वास्तुकला के साथ दोहरे प्रोसेसर सिस्टम के निर्माण के लिए एक इंटरफ़ेस लागू किया गया है (दूसरी पीढ़ी के पेंटियम से शुरू)।

- ऊर्जा प्रबंधन उपकरण पेश किए गए हैं।

- बस साइकिलों की पाइपलाइन एड्रेसिंग का उपयोग किया जाता है।

- निर्देशों को निष्पादित करने का समय (चक्रों की संख्या) कम कर दिया गया है।

- निर्देश अनुरेखण और प्रदर्शन निगरानी शुरू की गई है।

- वर्चुअल मोड की क्षमताओं का विस्तार किया गया है - इंटरप्ट फ़्लैग वर्चुअलाइजेशन पेश किया गया है।

- पेजिंग मोड में 4 एमबी पृष्ठों को संचालित करने की क्षमता पेश की गई है।

सभी पेंटियम प्रोसेसर में एसएमएम क्षमताएं होती हैं, जिनकी क्षमताओं का विस्तार नए मॉडलों के सामने आने के साथ हुआ है। परीक्षण सुविधाओं में माइक्रोकोड त्रुटियों, प्रोग्रामयोग्य तर्क सरणी, कमांड कैश, स्टोरेज कैश, फास्ट फॉरवर्ड बफर और रोम का पता लगाने के लिए अंतर्निहित बीआईएसटी (बिल्ट-इन सेल्फ टेस्ट) क्षमता शामिल है। सभी प्रोसेसर में एक मानक IEEE 1149.1 परीक्षण पोर्ट होता है, जो आपको JTAG इंटरफ़ेस का उपयोग करके प्रोसेसर का परीक्षण करने की अनुमति देता है।

प्रोसेसर ने नए अतिरिक्त डिबगिंग टूल लागू किए हैं:

- जांच मोड, जो पेंटियम प्रोसेसर सिस्टम मेमोरी के आंतरिक रजिस्टरों और I/O स्थानों तक पहुंच प्रदान करता है। यह मोड आपको सीपीयू की स्थिति की जांच करने और बदलने की अनुमति देता है, इन-सर्किट एमुलेटर के समान क्षमताओं वाले डिबगिंग प्रोग्राम के लिए एक साधन प्रदान करता है;

- डीई डिबगिंग एक्सटेंशन (डीबग एक्सटेंशन), जो आपको I/O पते पर ब्रेकप्वाइंट सेट करने की अनुमति देता है;

- प्रदर्शन की निगरानी और घटनाओं की संख्या रिकॉर्ड करने के लिए उपयोग किए जाने वाले आंतरिक काउंटर;

- CPUID कमांड का उपयोग करके चरण-दर-चरण निष्पादन।

60 और 66 मेगाहर्ट्ज की घड़ी आवृत्ति के साथ पहली पीढ़ी के पेंटियम प्रोसेसर (पी5) में 5 वी का आपूर्ति वोल्टेज था, जिसके कारण उच्च ताप उत्पादन (66 मेगाहर्ट्ज - 16 डब्ल्यू की आवृत्ति पर) हुआ। वे पीजीए-273 पैकेज (21x21 मैट्रिक्स) में उत्पादित किए गए थे, सॉकेट 4 इन प्रोसेसर को स्थापित करने के लिए है।

पहले प्रोसेसर मॉडल में एफपीयू (फ्लोटिंग पॉइंट दोष) में एक त्रुटि थी, जिसके परिणामस्वरूप ऑपरेंड के कुछ संयोजनों के साथ विभाजन करते समय सटीकता का नुकसान हुआ। त्रुटि दशमलव बिंदु के बाद चौथे से 19वें अंक तक दिखाई दे सकती है। 1995 की शुरुआत से, प्रोसेसर का उत्पादन त्रुटियों के बिना किया गया है। सांख्यिकीय अध्ययन से पता चलता है कि त्रुटि हर कुछ वर्षों में एक बार दिखाई दे सकती है। फिर भी, इंटेल अभी भी त्रुटि वाले पहले से ही बेचे गए प्रोसेसर को सही संस्करणों के साथ मुफ्त प्रतिस्थापन प्रदान करता है, लेकिन अधिक आधुनिक मॉडलों के लिए "अपग्रेड" के बिना। त्रुटियों वाले प्रोसेसर को CPUIDF.EXE उपयोगिता का उपयोग करके पहचाना जा सकता है, जिसे कंपनी के वेब सर्वर से प्राप्त किया जा सकता है।